# DESIGNING EFFICIENT MEMORY SCHEDULERS FOR FUTURE SYSTEMS

by

Niladrish Chatterjee

A dissertation submitted to the faculty of The University of Utah in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Computing

School of Computing

The University of Utah

December 2013

Copyright  $\bigodot$  Niladrish Chatterjee 2013

All Rights Reserved

# The University of Utah Graduate School

# STATEMENT OF DISSERTATION APPROVAL

| The dissertation of                                               | Nila       | adrish Chatterje | e                                                     |

|-------------------------------------------------------------------|------------|------------------|-------------------------------------------------------|

| has been approved by the following supervisory committee members: |            |                  |                                                       |

| Rajeev Balasubramo                                                | nian       | , Chair          | 30-Sept-2013<br>Date Approved                         |

| Alan Davis                                                        |            | , Member         | 30-Sept-2013                                          |

| Erik Brunvand                                                     |            | , Member         | Date Approved<br><b>30-Sept-2013</b><br>Date Approved |

| Nuwan Jayasena                                                    | L          | , Member         | 30-Sept-2013                                          |

| Naveen Muralimano                                                 | har        | , Member         | Date Approved 20-Oct-2013 Date Approved               |

| and by                                                            | Alan Davis |                  | , Chair/Dean of                                       |

| the Department/College/School of                                  |            | Computing        |                                                       |

and by David B. Kieda, Dean of The Graduate School.

# ABSTRACT

The internet-based information infrastructure that has powered the growth of modern personal/mobile computing is composed of powerful, warehouse-scale computers or datacenters. These heavily subscribed datacenters perform data-processing jobs under intense quality of service guarantees. Further, high-performance compute platforms are being used to model and analyze increasingly complex scientific problems and natural phenomena. To ensure that the high-performance needs of these machines are met, it is necessary to increase the efficiency of the memory system that supplies data to the processing cores. Many of the microarchitectural innovations that were designed to scale the memory wall (e.g., out-of-order instruction execution, on-chip caches) are being rendered less effective due to several emerging trends (e.g., increased emphasis on energy consumption, limited access locality). This motivates the optimization of the main memory system itself. The key to an efficient main memory system is the memory controller. In particular, the scheduling algorithm in the memory controller greatly influences its performance. This dissertation explores this hypothesis in several contexts. It develops tools to better understand memory scheduling and develops scheduling innovations for CPUs and GPUs. We propose novel memory scheduling techniques that are strongly aware of the access patterns of the clients as well as the microarchitecture of the memory device. Based on these, we present (i) a Dynamic Random Access Memory (DRAM) chip microarchitecture optimized for reducing write-induced slowdown, (ii) a memory scheduling algorithm that exploits these features, (iii) several memory scheduling algorithms to reduce the memory-related stall experienced by irregular General Purpose Graphics Processing Unit (GPGPU) applications, and (iv) the Utah Simulated Memory Module (USIMM), a detailed, validated simulator for DRAM main memory that we use for analyzing and proposing scheduler algorithms.

To My Parents, Wife, and the Taxpayers Who Subsidized My University Education

# CONTENTS

| ABS | STRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | iii                                                                                                                                                 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| LIS | T OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ix                                                                                                                                                  |

| ACI | KNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | x                                                                                                                                                   |

| CH  | APTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                     |

| 1.  | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                   |

|     | <ul> <li>1.1 Emerging Trends</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $     \begin{array}{c}       1 \\       1 \\       2 \\       3 \\       3 \\       3 \\       5 \\       5 \\       6 \\       7     \end{array} $ |

| 2.  | BACKGROUND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8                                                                                                                                                   |

|     | <ul> <li>2.1 Memory System Basics</li> <li>2.1.1 DRAM System Organization</li> <li>2.1.2 Memory Controller</li> <li>2.1.2.1 Address Translation</li> <li>2.1.2.2 Memory Scheduling</li> <li>2.1.2.3 Error Management</li> <li>2.1.3 Main Memory Scheduling</li> <li>2.1.3.1 Memory Access Protocol</li> <li>2.1.3.2 Transaction Scheduling</li> <li>2.1.3.3 Write Scheduling</li> <li>2.1.3.4 Command Scheduler</li> <li>2.2 Graphics Processing Unit Basics</li> <li>2.3 Scheduling Background</li> <li>2.3.1 First Read First-Come-First-Served (FR-FCFS)</li> <li>2.3.2 Stall-Time Fair Memory-Scheduling (STFM)</li> <li>2.3.3 Parallelism-Aware Batch Scheduling (PARBS)</li> <li>2.3.4 Adaptive per-Thread Least-Attained-Service</li> </ul> |                                                                                                                                                     |

|     | Memory Scheduling (ATLAS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $\begin{array}{c} 17\\17\end{array}$                                                                                                                |

|    | 2.3.6 Scheduling with Processor-Side<br>Load Criticality Information                                                           | 17                                     |

|----|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|    | 2.3.7 Staged Memory Scheduling (SMS)                                                                                           | 18                                     |

| 3. | A DRAM SCHEDULER OPTIMIZED FOR WRITES                                                                                          | 19                                     |

|    | <ul> <li>3.1 Impact of DRAM Writes on Reads</li></ul>                                                                          | 19<br>21<br>21                         |

|    | 3.2.1       Main Memory Dackground         3.2.2       Simulation Methodology         3.2.3       Motivational Results         | $\frac{21}{22}$                        |

|    | 3.3 Staged Reads       3.3.1 Proposed Memory Access Pipeline         3.3.1.1 Baseline Scheduling       3.3.1.1                 | 26<br>26<br>26                         |

|    | 3.3.1.1       Dasenne Scheduning         3.3.1.2       Optimization Opportunity         3.3.1.3       Timing with Staged Reads | 20<br>27<br>28                         |

|    | 3.3.2       Staged Read Implementation         3.3.2.1       Area Overhead         3.3.2.2       Effect on Regular Reads       | 28<br>30<br>31                         |

|    | 3.3.2.2       Enect on Regular Reads         3.3.2.3       New Memory Commands         3.3.2.4       Implementability          | 31<br>31<br>31                         |

|    | 3.3.2.5 Targeting Niche Markets3.3.3 Exploiting Staged Reads—Memory Scheduler3.4 Evaluation                                    | 32<br>32<br>33                         |

|    | 3.4.1 Results       3.4.2 Sensitivity Analysis                                                                                 | зэ<br>33<br>39                         |

|    | 3.4.2.1Write Queue Parameters3.4.2.2More Banks3.4.3Projecting for Future Main Memory Trends                                    | 39<br>42<br>43                         |

|    | 3.4.3.1Higher Write Traffic3.4.3.2Phase Change Memory (PCM)                                                                    | 43<br>43<br>44                         |

|    | 3.4.3.3       Number of Channels         3.5       Conclusions                                                                 | $\begin{array}{c} 45\\ 45 \end{array}$ |

| 4. | A DRAM SCHEDULER OPTIMIZED FOR GPUS                                                                                            | 47                                     |

|    | 4.1 Introduction       4.2 Background         4.2 Background       4.2.1 GPU Cores                                             | $47 \\ 49 \\ 49$                       |

|    | <ul> <li>4.2.2 Memory System</li></ul>                                                                                         | $50 \\ 51 \\ 51$                       |

|    | 4.2.3.2Baseline Scheduling Policy4.3Warp-Aware Memory Schedulers4.3.1Warp-Aware Memory Controller Organization                 | 52<br>53<br>54                         |

|    | <ul><li>4.3.2 Warp-Aware FCFS (WAFCFS)</li></ul>                                                                               | $\frac{54}{56}$                        |

|    | 4.3.3.1Scoring System4.3.3.2BASJF Transaction Scheduling Policy4.3.4Scheduling for Multiple Memory Controllers                 | $56 \\ 57 \\ 58$                       |

|    | vi                                                                                                                             |                                        |

| 4.3.5 Improving the Performance of BASJF+AB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 59                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.3.5.1 Estimating MERB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60                                                                                                                                                       |

| 4.3.6 Warp-Aware Write Draining (WAWD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 61                                                                                                                                                       |

| 4.3.7 Hardware Overhead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 62                                                                                                                                                       |

| 4.3.8 Summary of Proposed Schemes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63                                                                                                                                                       |

| 4.4 Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 64                                                                                                                                                       |

| 4.5 Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 65                                                                                                                                                       |

| 4.5.1 Impact on Type-1 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 65                                                                                                                                                       |

| 4.5.1.1 WAFCFS:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 66                                                                                                                                                       |

| 4.5.1.2 BASJF:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 67                                                                                                                                                       |

| 4.5.1.3 BASJF+AB:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 68                                                                                                                                                       |

| 4.5.1.4 MERB:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 69                                                                                                                                                       |

| 4.5.1.5 WAWD:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 70                                                                                                                                                       |

| 4.5.2 Impact on Type-2 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 71                                                                                                                                                       |

| 4.5.3 Comparison with Single-Bank Warp-Aware Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72                                                                                                                                                       |

| 4.6 Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 74                                                                                                                                                       |

| 4.6.1 Memory Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 74                                                                                                                                                       |

| 4.6.2 GPU Memory Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 74                                                                                                                                                       |

| 4.6.3 PAR-BS:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 74                                                                                                                                                       |

| 4.6.4 ATLAS:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 75                                                                                                                                                       |

| 4.6.5 Memory Divergence Mitigation in GPUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 75                                                                                                                                                       |

| 4.7 Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 75                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                          |

| 5.1 Simulator Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 77<br>77                                                                                                                                                 |

| 5.1.1 High-Level Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 77<br>77<br>78                                                                                                                                           |

| 5.1.1 High-Level Overview5.1.2 Code Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 77                                                                                                                                                       |

| 5.1.1 High-Level Overview         5.1.2 Code Files         5.1.3 Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 77<br>78                                                                                                                                                 |

| 5.1.1 High-Level Overview         5.1.2 Code Files         5.1.3 Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 77<br>78<br>78                                                                                                                                           |

| <ul> <li>5.1.1 High-Level Overview</li> <li>5.1.2 Code Files</li> <li>5.1.3 Inputs</li> <li>5.1.4 Simulation Cycle</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 77<br>78<br>78<br>78                                                                                                                                     |

| 5.1.1 High-Level Overview         5.1.2 Code Files         5.1.3 Inputs         5.1.4 Simulation Cycle.         5.1.5 Commit         5.1.6 Checking for Readiness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 77<br>78<br>78<br>78<br>78<br>79                                                                                                                         |

| 5.1.1 High-Level Overview         5.1.2 Code Files         5.1.3 Inputs         5.1.4 Simulation Cycle.         5.1.5 Commit         5.1.6 Checking for Readiness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 77<br>78<br>78<br>78<br>79<br>79                                                                                                                         |

| 5.1.1 High-Level Overview         5.1.2 Code Files         5.1.3 Inputs         5.1.4 Simulation Cycle.         5.1.5 Commit         5.1.6 Checking for Readiness         5.1.7 Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 77<br>78<br>78<br>78<br>79<br>79<br>79                                                                                                                   |

| 5.1.1 High-Level Overview         5.1.2 Code Files         5.1.3 Inputs         5.1.4 Simulation Cycle.         5.1.5 Commit         5.1.6 Checking for Readiness         5.1.7 Scheduling         5.1.8 Instruction Completion Times                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 77<br>78<br>78<br>78<br>79<br>79<br>79<br>79<br>80                                                                                                       |

| 5.1.1 High-Level Overview5.1.2 Code Files5.1.3 Inputs5.1.4 Simulation Cycle.5.1.5 Commit5.1.6 Checking for Readiness5.1.7 Scheduling5.1.8 Instruction Completion Times5.1.9 Advancing the Trace and Trace Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 77<br>78<br>78<br>78<br>79<br>79<br>79<br>80<br>80                                                                                                       |

| 5.1.1 High-Level Overview5.1.2 Code Files5.1.3 Inputs5.1.4 Simulation Cycle.5.1.5 Commit5.1.6 Checking for Readiness5.1.7 Scheduling5.1.8 Instruction Completion Times5.1.9 Advancing the Trace and Trace Format5.1.10 Fetch Constraints and Write Drains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 77<br>78<br>78<br>78<br>79<br>79<br>79<br>80<br>80<br>80                                                                                                 |

| 5.1.1 High-Level Overview5.1.2 Code Files5.1.3 Inputs5.1.4 Simulation Cycle.5.1.5 Commit5.1.6 Checking for Readiness5.1.7 Scheduling5.1.8 Instruction Completion Times5.1.9 Advancing the Trace and Trace Format5.1.10 Fetch Constraints and Write Drains5.1.11 Refresh Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $77 \\ 78 \\ 78 \\ 78 \\ 79 \\ 79 \\ 79 \\ 80 \\ 80 \\ 80 \\ 81$                                                                                         |

| 5.1.1High-Level Overview5.1.2Code Files5.1.3Inputs5.1.4Simulation Cycle.5.1.5Commit5.1.6Checking for Readiness5.1.7Scheduling5.1.8Instruction Completion Times5.1.9Advancing the Trace and Trace Format5.1.10Fetch Constraints and Write Drains5.1.11Refresh Handling5.1.12Implicit Scheduling Constraints5.1.13Address Mapping5.1.14Example Schedulers                                                                                                                                                                                                                                                                                                                                                                                             | 77<br>78<br>78<br>78<br>79<br>79<br>79<br>79<br>80<br>80<br>80<br>80<br>81<br>81                                                                         |

| <ul> <li>5.1.1 High-Level Overview</li> <li>5.1.2 Code Files</li> <li>5.1.3 Inputs</li> <li>5.1.4 Simulation Cycle.</li> <li>5.1.5 Commit</li> <li>5.1.6 Checking for Readiness</li> <li>5.1.7 Scheduling</li> <li>5.1.8 Instruction Completion Times</li> <li>5.1.9 Advancing the Trace and Trace Format</li> <li>5.1.10 Fetch Constraints and Write Drains</li> <li>5.1.11 Refresh Handling</li> <li>5.1.12 Implicit Scheduling Constraints</li> <li>5.1.13 Address Mapping</li> </ul>                                                                                                                                                                                                                                                            | $77 \\ 78 \\ 78 \\ 79 \\ 79 \\ 79 \\ 80 \\ 80 \\ 80 \\ 81 \\ 81 \\ 82$                                                                                   |

| 5.1.1High-Level Overview5.1.2Code Files5.1.3Inputs5.1.4Simulation Cycle.5.1.5Commit5.1.6Checking for Readiness5.1.7Scheduling5.1.8Instruction Completion Times5.1.9Advancing the Trace and Trace Format5.1.10Fetch Constraints and Write Drains5.1.11Refresh Handling5.1.12Implicit Scheduling Constraints5.1.13Address Mapping5.1.14Example Schedulers                                                                                                                                                                                                                                                                                                                                                                                             | $\begin{array}{c} 77\\ 78\\ 78\\ 78\\ 79\\ 79\\ 79\\ 80\\ 80\\ 80\\ 80\\ 81\\ 81\\ 82\\ 82\\ 82\end{array}$                                              |

| <ul> <li>5.1.1 High-Level Overview</li> <li>5.1.2 Code Files</li> <li>5.1.3 Inputs</li> <li>5.1.4 Simulation Cycle.</li> <li>5.1.5 Commit</li> <li>5.1.6 Checking for Readiness</li> <li>5.1.7 Scheduling</li> <li>5.1.8 Instruction Completion Times</li> <li>5.1.9 Advancing the Trace and Trace Format</li> <li>5.1.10 Fetch Constraints and Write Drains</li> <li>5.1.11 Refresh Handling</li> <li>5.1.12 Implicit Scheduling Constraints</li> <li>5.1.13 Address Mapping</li> <li>5.1.14 Example Schedulers</li> <li>5.1.14.1 FCFS, scheduler-fcfs.c</li> </ul>                                                                                                                                                                                | $\begin{array}{c} 77\\ 78\\ 78\\ 78\\ 79\\ 79\\ 79\\ 80\\ 80\\ 80\\ 80\\ 81\\ 81\\ 81\\ 82\\ 82\\ 82\\ 82\end{array}$                                    |

| <ul> <li>5.1.1 High-Level Overview</li> <li>5.1.2 Code Files</li> <li>5.1.3 Inputs</li> <li>5.1.4 Simulation Cycle.</li> <li>5.1.5 Commit</li> <li>5.1.6 Checking for Readiness</li> <li>5.1.7 Scheduling</li> <li>5.1.8 Instruction Completion Times</li> <li>5.1.8 Instruction Completion Times</li> <li>5.1.9 Advancing the Trace and Trace Format</li> <li>5.1.10 Fetch Constraints and Write Drains</li> <li>5.1.11 Refresh Handling</li> <li>5.1.12 Implicit Scheduling Constraints</li> <li>5.1.13 Address Mapping</li> <li>5.1.14 Example Schedulers</li> <li>5.1.14.1 FCFS, scheduler-fcfs.c</li> <li>5.1.14.2 Credit-Fair, scheduler-creditfair.c</li> <li>5.1.14.4 Close-Page, scheduler-close.c</li> </ul>                              | $\begin{array}{c} 77\\ 78\\ 78\\ 78\\ 79\\ 79\\ 79\\ 80\\ 80\\ 80\\ 80\\ 81\\ 81\\ 82\\ 82\\ 82\\ 82\\ 83\\ 83\\ 83\\ 83\\ 83\end{array}$                |

| <ul> <li>5.1.1 High-Level Overview</li> <li>5.1.2 Code Files</li> <li>5.1.3 Inputs</li> <li>5.1.4 Simulation Cycle.</li> <li>5.1.5 Commit</li> <li>5.1.6 Checking for Readiness</li> <li>5.1.7 Scheduling</li> <li>5.1.8 Instruction Completion Times</li> <li>5.1.9 Advancing the Trace and Trace Format</li> <li>5.1.10 Fetch Constraints and Write Drains</li> <li>5.1.11 Refresh Handling</li> <li>5.1.12 Implicit Scheduling Constraints</li> <li>5.1.14 Example Schedulers</li> <li>5.1.14.1 FCFS, scheduler-fcfs.c</li> <li>5.1.14.3 Power-Down, scheduler-pwrdn.c</li> <li>5.1.14.5 First-Ready-Round-Robin, scheduler-frrr.c</li> </ul>                                                                                                    | $\begin{array}{c} 77\\ 78\\ 78\\ 78\\ 79\\ 79\\ 79\\ 80\\ 80\\ 80\\ 80\\ 81\\ 81\\ 82\\ 82\\ 82\\ 82\\ 83\\ 83\\ 83\\ 83\\ 83\\ 83\\ 83\\ 83\\ 83\\ 83$  |

| <ul> <li>5.1.1 High-Level Overview</li> <li>5.1.2 Code Files</li> <li>5.1.3 Inputs</li> <li>5.1.4 Simulation Cycle.</li> <li>5.1.5 Commit</li> <li>5.1.6 Checking for Readiness</li> <li>5.1.7 Scheduling</li> <li>5.1.8 Instruction Completion Times</li> <li>5.1.9 Advancing the Trace and Trace Format</li> <li>5.1.10 Fetch Constraints and Write Drains</li> <li>5.1.11 Refresh Handling</li> <li>5.1.12 Implicit Scheduling Constraints</li> <li>5.1.14 Example Schedulers</li> <li>5.1.14.1 FCFS, scheduler-fcfs.c</li> <li>5.1.14.3 Power-Down, scheduler-pwrdn.c</li> <li>5.1.14.5 First-Ready-Round-Robin, scheduler-frrr.c</li> <li>5.1.14.6 MLP-aware, scheduler-mlp.c</li> </ul>                                                       | $\begin{array}{c} 77\\ 78\\ 78\\ 78\\ 79\\ 79\\ 79\\ 80\\ 80\\ 80\\ 80\\ 81\\ 81\\ 82\\ 82\\ 82\\ 83\\ 83\\ 83\\ 83\\ 83\\ 84\\ \end{array}$             |

| <ul> <li>5.1.1 High-Level Overview</li> <li>5.1.2 Code Files</li> <li>5.1.3 Inputs</li> <li>5.1.4 Simulation Cycle.</li> <li>5.1.5 Commit</li> <li>5.1.6 Checking for Readiness</li> <li>5.1.7 Scheduling</li> <li>5.1.8 Instruction Completion Times</li> <li>5.1.9 Advancing the Trace and Trace Format</li> <li>5.1.10 Fetch Constraints and Write Drains</li> <li>5.1.11 Refresh Handling</li> <li>5.1.12 Implicit Scheduling Constraints</li> <li>5.1.14 Example Schedulers</li> <li>5.1.14.1 FCFS, scheduler-fcfs.c</li> <li>5.1.14.2 Credit-Fair, scheduler-creditfair.c</li> <li>5.1.14.3 Power-Down, scheduler-pwrdn.c</li> <li>5.1.14.5 First-Ready-Round-Robin, scheduler-frrr.c</li> <li>5.1.14.6 MLP-aware, scheduler-mlp.c</li> </ul> | $\begin{array}{c} 77\\ 78\\ 78\\ 78\\ 79\\ 79\\ 79\\ 80\\ 80\\ 80\\ 80\\ 81\\ 81\\ 82\\ 82\\ 82\\ 82\\ 83\\ 83\\ 83\\ 83\\ 83\\ 84\\ 84\\ 84\end{array}$ |

| <ul> <li>5.1.1 High-Level Overview</li> <li>5.1.2 Code Files</li> <li>5.1.3 Inputs</li> <li>5.1.4 Simulation Cycle.</li> <li>5.1.5 Commit</li> <li>5.1.6 Checking for Readiness</li> <li>5.1.7 Scheduling</li> <li>5.1.8 Instruction Completion Times</li> <li>5.1.9 Advancing the Trace and Trace Format</li> <li>5.1.10 Fetch Constraints and Write Drains</li> <li>5.1.11 Refresh Handling</li> <li>5.1.12 Implicit Scheduling Constraints</li> <li>5.1.14 Example Schedulers</li> <li>5.1.14.1 FCFS, scheduler-fcfs.c</li> <li>5.1.14.3 Power-Down, scheduler-pwrdn.c</li> <li>5.1.14.5 First-Ready-Round-Robin, scheduler-frrr.c</li> <li>5.1.14.6 MLP-aware, scheduler-mlp.c</li> </ul>                                                       | $\begin{array}{c} 77\\ 78\\ 78\\ 78\\ 79\\ 79\\ 79\\ 80\\ 80\\ 80\\ 80\\ 81\\ 81\\ 82\\ 82\\ 82\\ 83\\ 83\\ 83\\ 83\\ 83\\ 84\\ \end{array}$             |

|    | 5.3 DRAM Power Model                                                                                                   | 88                       |

|----|------------------------------------------------------------------------------------------------------------------------|--------------------------|

|    | 5.3.1 Memory Organizations                                                                                             | 88                       |

|    | 5.3.2 Power Equations                                                                                                  | 88                       |

|    | 5.3.3 System Power Model                                                                                               | 91                       |

|    | 5.4 Using USIMM                                                                                                        | 91                       |

|    | 5.5 Validation Against Micron DDR3 Verilog Models                                                                      | 92                       |

|    | 5.6 Alternative Software Architecture                                                                                  | 95                       |

|    | 5.7 Integrating USIMM with a Full-System Simulator                                                                     | 96                       |

|    |                                                                                                                        |                          |

| 6. | CONCLUSION AND FUTURE WORK 1                                                                                           | L <b>01</b>              |

| 6. | CONCLUSION AND FUTURE WORK       1         6.1 Contributions       1                                                   |                          |

| 6. |                                                                                                                        | 101                      |

| 6. | 6.1 Contributions                                                                                                      | 101<br>104               |

| 6. | 6.1 Contributions    1      6.2 Future Work    1                                                                       | 101<br>104<br>104        |

| 6. | 6.1 Contributions       1         6.2 Future Work       1         6.2.1 Scheduling for Heterogeneous Platforms       1 | 101<br>104<br>104<br>104 |

# LIST OF TABLES

| 3.1 | Simulator parameters.                                          | 23 |

|-----|----------------------------------------------------------------|----|

| 3.2 | Timing parameters.                                             | 24 |

| 4.1 | Simulation Parameters                                          | 64 |

| 4.2 | Workloads                                                      | 66 |

| 5.1 | DRAM timing parameters for default memory system configuration | 86 |

| 5.2 | Command timing restrictions                                    | 87 |

| 5.3 | Different memory configurations in our power model             | 89 |

| 5.4 | Voltage and current parameters of modeled chips                | 90 |

| 5.5 | System configurations used for the JWAC MSC                    | 93 |

| 5.6 | USIMM workloads                                                | 94 |

| 5.7 | Fudge values                                                   | 99 |

# ACKNOWLEDGEMENTS

A PhD is the culmination of frantic efforts over a long period of time. At times during these five years, things looked great; ideas were forming in dreams and in the shower, experiments were producing good results, bugs were fixing themselves, and papers were waltzing into conferences. But interspersed with these rosy times, there were times when, to quote Al Davis, the PhD experience felt like "setting your hair on fire for five years." Times like these are what make up the real PhD experience. I am extremely thankful for having people around me who reminded me, during these times, that there is a world outside my cubicle in the Utah Arch lab. My wife Anusua and my parents managed to find the right balance of sweet cajoling and brisk rebuke to set me straight whenever I tried to emulate the proverbial headless chicken during these five years. There is simply no way in which I could have made progress without their willingness to bear with my erratic behavior with unshakeable good demeanor.

Having a good PhD advisor might be the single-biggest factor in determining the quality and success of a graduate career. I had the best. Rajeev's technical acumen is known very well in academic circles. But more importantly, his quick sense of humor, calmness, balance in life, and innate humility have had the biggest effects on me, and I hope to emulate these aspects of his personality throughout my career as well.

My committee members have also had a big impact on the quality and scope of my work. I am thankful for the advice I received from Al and Erik that comes from their years of experience in dealing with complex problems and problematic grad students. Nuwan gave me the chance to intern for AMD Research, where I learned a great deal from him and made friends I would not have made otherwise. I would also like to take this opportunity to thank Mike O'Connor and Gabriel Loh at AMD, whose technical insight helped me to formulate a lot of the ideas in this thesis. Naveen was a senior PhD student in the Utah Arch lab when I joined, a mentor to me during my internship at HP Labs under Norm Jouppi, and finally became my committee member. He has provided invaluable advice on my research, on my course selection, on my job search, and on restaurants in the Bay Area.

My labmates from the Utah Arch labaratory are an "interesting" bunch, to put it mildly. Kshitij, Manu, Ani, Dave, Seth, Manju, Ali, Danny, and Aasheesh have been collaborators at work and partners in crime—catch me sometime to hear about some of the literally insane experiences we have shared together. My friends in Salt Lake City, Arijit, Protonu, Saurav, Meghana, Piyush, and Avishek increased my quality of life immensely and made it possible to enjoy the incredible landscape of this scenic state. My good friend Syamantak Das was the first to motivate me to get into a graduate program and a great pillar of support over instant-messenger.

Finally I would like to thank Karen and Ann at the School of Computing for their advice and help in keeping me in line with the plethora of official rules that dictate the lives of all international students.

# CHAPTER 1

# INTRODUCTION

### **1.1** Emerging Trends

Current trends indicate that the computing industry will bifurcate primarily along the following lines. The first kind of computers will be the relatively simple mobile devices that act as information consumption terminals. The other kind will be deployed in large server farms, also called warehouse-scale computers. The mobile devices are severely constrained by their form-factors and battery-life, and are thus reliant on a web-based information distribution infrastructure for their operation. The intensive computing required to provide these mobile devices with data will be carried out in powerful computers in large datacenters. On the other hand, scientific and high-performance computing tasks will be carried out on increasingly powerful machines which support a high degree of parallelism. One of the major challenges in architecting such powerful systems is the efficient delivery of data to the compute cores. The main memory system has always been a system bottleneck. In particular, the memory latency wall has been a well-recognized issue. Many important innovations in processor microarchitecture, e.g., out-of-order speculative processing, symmetric multithreading, and branch-prediction, have tried to leverage instruction-level-parallelism to mitigate the latency wall. On the other hand, multicore processors and graphics processing units have looked to leverage thread-level parallelism to hide memory-induced delays. However, several emerging trends are threatening to reduce the efficiency of these established techniques, and, consequently, motivating the optimization of the main memory system itself.

#### 1.1.1 Energy Constraints Forcing Simpler Cores

A large datacenter housing several thousands of servers can consume up to 30 MW of power [1] and the combined energy consumption of datacenters accounts for about

2% of the total energy production in the United States [2]. Processors are the highest consumers of energy in such systems. The large reorder buffers and other associated mechanisms that enable out-of-order processing have often been singled out for high power consumption. This has led to the use of simpler processor cores in servers, such as Intel's Atom [3] and more commonly, low-power Advanced RISC Machines (ARM) cores [4]. Many of these simpler cores offer limited to no support for out-of-order processing. Since the processors cannot effectively hide the Dynamic Random Accem Memory (DRAM) latency, performance-optimized main memory becomes a necessity.

#### 1.1.2 Performance Demands of the Future

The performance demand from servers is always on the rise. The most exciting commercial applications of today are in the field of "big data." This model of computation typically requires the mining of useful insight and information from many thousands of petabytes of data. Thousands of threads mining this data can be run concurrently on the hardware thanks to the increasing on-chip core counts. Also, general purpose GPUs (GPGPUs) are being employed increasingly in highperformance-computing platforms to model complex natural phenomena and also in commercial compute systems as data-parallel accelerators. The high degree of thread-parallelism exerts tremendous pressure on the memory bandwidth. DRAM vendors have responded to this challenge by increasing the DRAM pin frequency. In spite of this, the aggregate available bandwidth is limited by the pin count on the processor socket. Compared to the 16X growth that is expected to take place in transistor count (and probably on-chip core count) over a period of 8 years, pin counts are estimated to grow by only 1.47X in the same period, according to the ITRS road-map [5]. With several cores competing for the restricted number of pins, it is more important than ever to increase the bandwidth utilization and reduce the high queuing delay encountered by memory requests. The bandwidth utilization is a function of the DRAM bank utilization which motivates intelligent memory controllers.

#### 1.1.3 DRAM Core Speeds

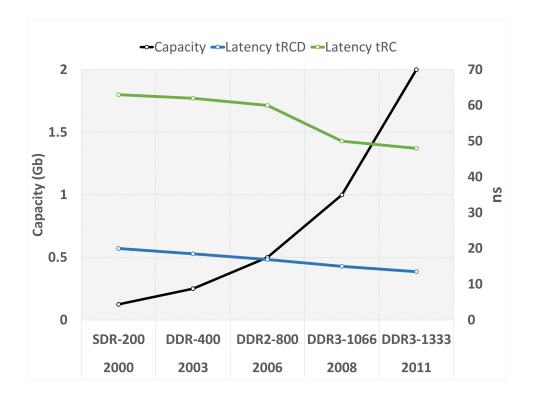

The DRAM pin bandwidth (i.e., DRAM interface frequency) has increased significantly over different DRAM generations; the same cannot be said about the DRAM core latencies. Fig. 1.1 demonstrates how two of the most important timing parameters that determine DRAM latency have reduced only slightly over the years. As a consequence, while the latency for transmitting a set of bits over the DRAM interface to the processor has reduced (owing to the increasing data-rates shown on the x-axis of Fig. 1.1), the latency of accessing the DRAM core has not scaled. In high-traffic scenarios, this increases contention for the DRAM banks (see Chapter 2), leading to higher overall latency.

#### 1.1.4 Emerging Application Trends

Applications of the future demand high performance and higher reliability. Modern GPUs allow developers to express the parallelism in their applications through programming paradigms like CUDA [6] and OpenCL [7]. While GPUs are well-suited for handling regular, structured code, it is still a large challenge to efficiently support irregular applications [8]. The GPU core and memory architecture are organized with expectations of regular compute and access patterns and can lead to significant performance penalties for irregular applications.

On the other hand, datacenters running business-critical applications require reliable memory systems. This has led to the deployment of chipkill-correct memory systems [9] where the memory system is able to tolerate the failure of a complete DRAM chip. A direct consequence of the chipkill feature is an increase in the write-traffic to the memory system. Most DRAM systems are designed to primarily accelerate reads (as writes are not on the critical path), but inefficient handling of writes can cause large slowdowns.

## 1.2 Dissertation Overview

It is clear from the preceding discussion that the memory latency wall continues to be a major concern. In this dissertation, we look at optimizations to the memory system that can satisfy the performance demands of future workloads. To accomplish this, we focus on the memory controller, which constitutes the "smarts" of the main

Figure 1.1. DRAM Trends

memory system and is also the most malleable part of the memory system where changes can be instituted with minimum cost impacts. The impact of memory scheduling algorithms on overall system throughput and power consumption have been demonstrated by previous studies [10], [11], [12], [13], [14], [15]. However, very few studies have looked at the impact of write scheduling on DRAM reads [16], [17]. We find that writes can be a significant bottleneck in current workloads and certainly in future systems that employ more stringent error checking and in systems that deploy nonvolatile memory chips. We design a memory architecture to mitigate this bottleneck. Similarly, memory scheduling techniques for GPU architectures have focused on improving the memory throughput with little consideration of the impact of DRAM latency on GPU performance. We show that in Single Instruction Multiple Thread (SIMT) cores, the memory system needs to be aware of the source of requests during the scheduling stage and invent mechanisms that provide high performance. Finally, we develop a detailed memory simulator that helps accelerate similar studies by the community at large. Our analysis with this simulator helps shed insight on memory scheduling bottlenecks.

#### 1.2.1 Thesis Statement

Main memory performance is a key determinant of system throughput. The most malleable part of the memory system is the memory controller. The key to architecting efficient memory for the future lies in the design of intelligent memory scheduling algorithms that are aware of memory access patterns and the intricacies of DRAM chip microarchitecture as well as the architectural bottlenecks in the client cores. This thesis is aimed at developing scheduling strategies and tools to address these issues.

#### 1.2.2 Write-Aware Main Memory

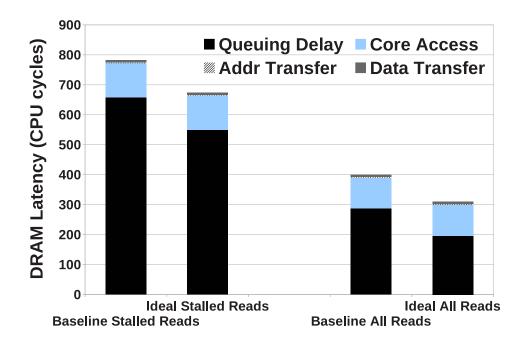

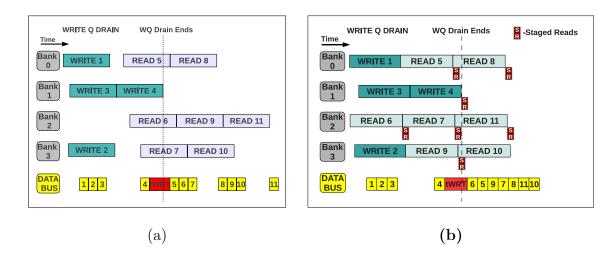

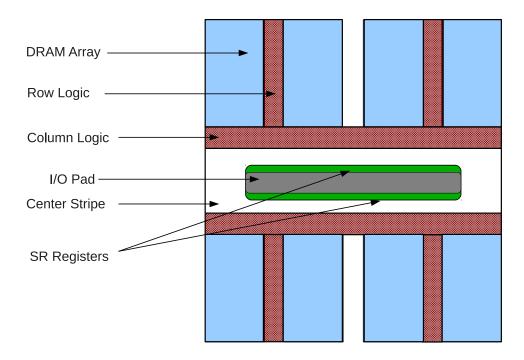

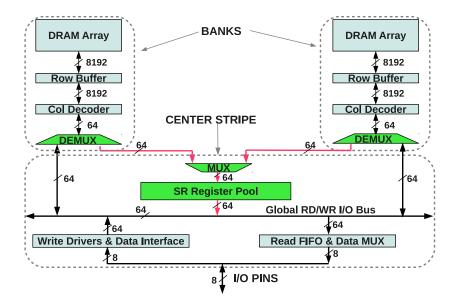

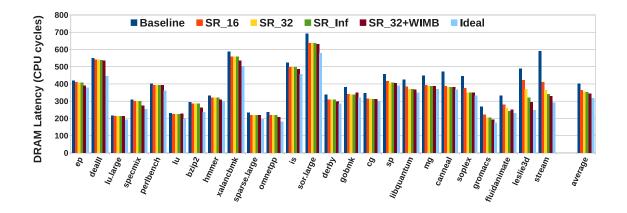

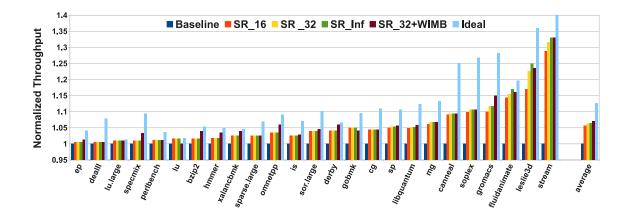

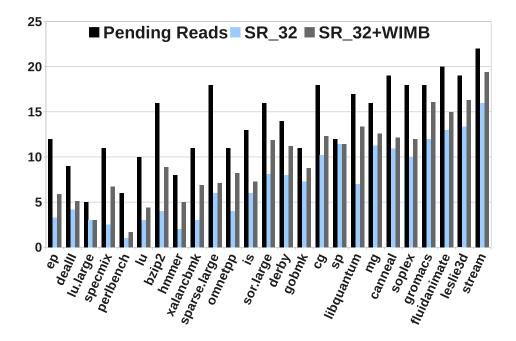

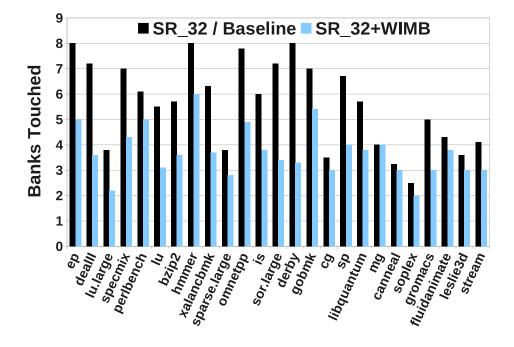

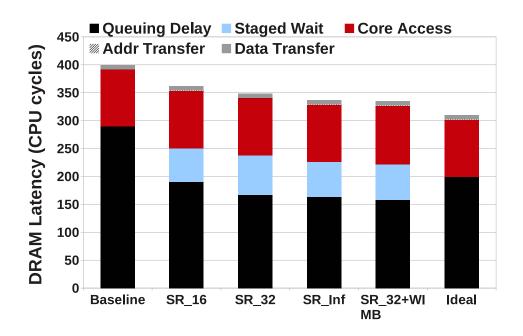

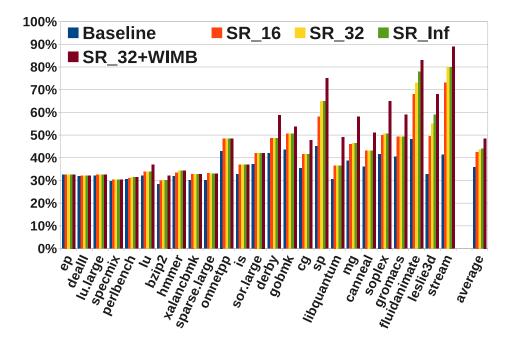

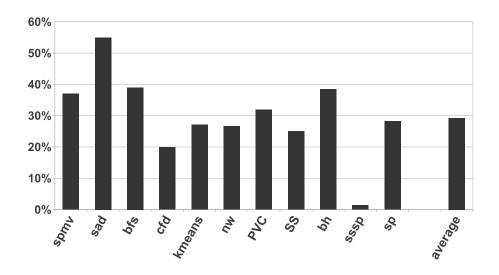

DRAM bandwidth is a precious system resource, and one of the factors that can prevent efficient utilization of the DRAM bandwidth is the draining of writes. Given that reads are on the critical path for CPU progress, reads are prioritized over DRAM writes by the memory scheduler, but writes have to be drained from the write queue buffers eventually and the write-drain process delays pending reads. In fact, a single channel in the main memory system offers almost no parallelism between reads and writes. This is because a single off-chip memory bus is shared by reads and writes, and the direction of the bus has to be explicitly turned around when switching from writes to reads. This is an expensive operation, and its cost is amortized by carrying out a burst of writes or reads every time the bus direction is switched. As a result, no reads can be processed while a memory channel is busy servicing writes even if the reads and writes are being serviced from different banks of the DRAM device. To alleviate this performance loss, we propose a novel mechanism to boost read-write parallelism and perform useful components of read operations even when the memory system is busy performing writes. If some of the banks are busy servicing writes, we start issuing reads to the other idle banks. The results of these reads are stored in a few registers near the memory chip's I/O pads. These results are quickly returned immediately following the bus turnaround. This reduces the queuing delay of the reads waiting for the write-queue drain to complete and also frees up banks faster for future reads. This process is referred to as a Staged Read because it decouples a single column-read operation into two stages, with the first step being performed in parallel with writes. This technique works well when there is bank imbalance in the write stream and there are pending reads on the banks that do not have many pending writes. To exploit this, we designed a write scheduling algorithm that artificially introduces bank imbalance and allows useful read operations to be performed during the write-drain. With a marginal chip area overhead (0.25%), we can gain a DRAM access latency improvement of 17% using staged-reads.

#### 1.2.3 Warp-Aware Main Memory

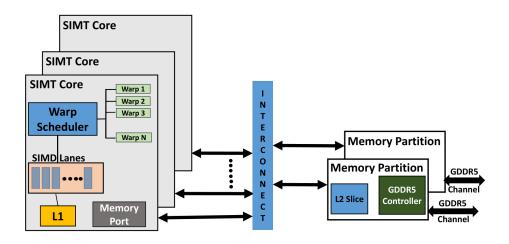

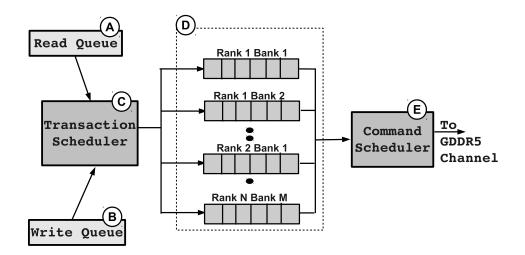

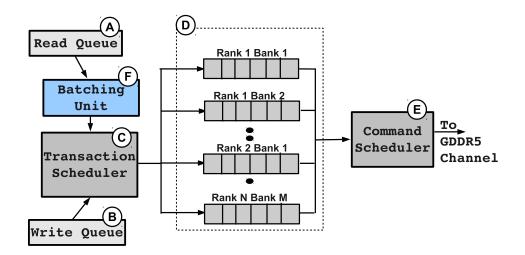

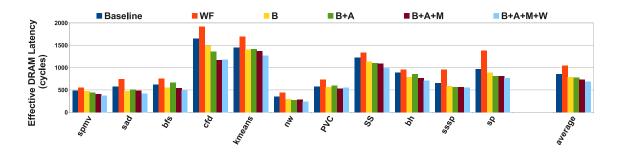

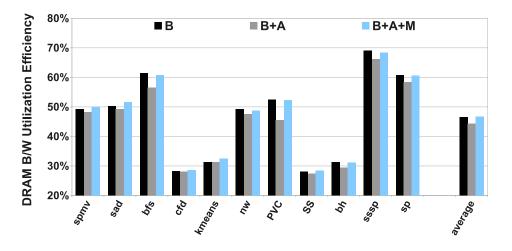

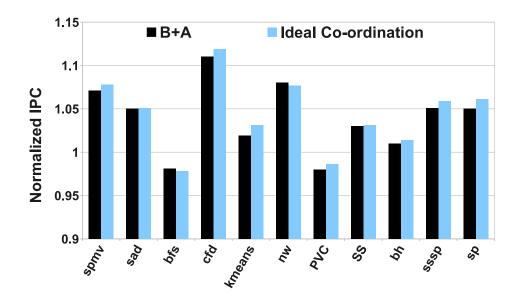

Graphics Processing Units (GPUs) use the SIMT model of computation where a group of threads execute the same instruction on different data elements. A group of threads running in lockstep in such a setup is called a warp (or a wavefront)—with every thread in the warp executing the same instruction. A load instruction in such a SIMT system can generate many different memory requests and the warp becomes ready to run (referred to hereafter as runnable) only when all of the outstanding memory requests are returned to the compute unit. The compute units are simple and typically lack the ability to hide the latencies of pending memory requests through techniques commonly found in out-of-order, speculative, superscalar processors. To negotiate long memory access times, a GPU's compute unit uses thread level parallelism instead of instruction level parallelism as a CPU would. Thus, when a warp waits for its memory requests to return from the memory system, the thread scheduler in the GPU picks a different warp that is ready to run. The memory requests issued by a warp will typically encounter different memory latencies. In fact, modern memory controllers schedule incoming requests out-of-order to maximize memory system throughput, which can stall some requests from a warp for a long time, thereby hampering the progress of the warp. This introduces the problem of memory latency divergence where a warp is stalled until the last memory request from a vector load instruction is returned to the compute unit. Several studies have highlighted how memory divergence can be a significant performance bottleneck in GPUs [18], [19]. We observe that the effective DRAM latency for a warp is often lengthened at the main memory because one or more requests of that warp are returned with longer latencies than the rest. We propose DRAM scheduling strategies that attempt to reduce the intrawarp memory latency divergence by eliminating interwarp interference. We first propose schemes that reduce intrawarp latency divergence in a single controller

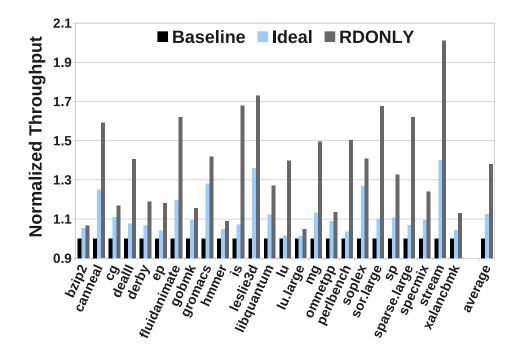

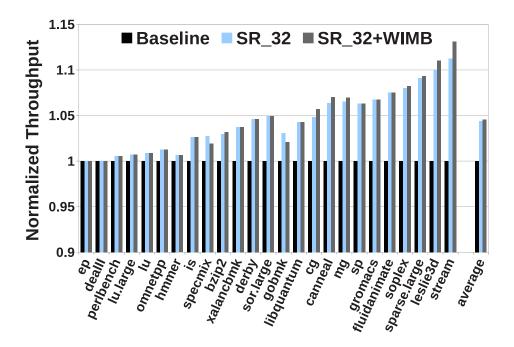

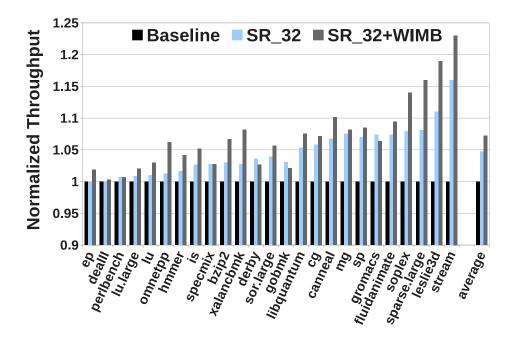

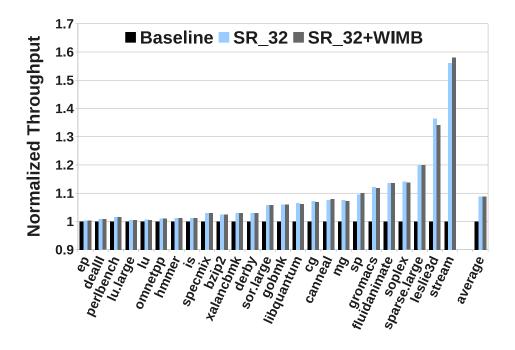

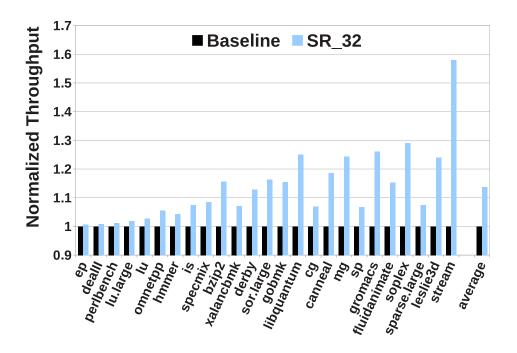

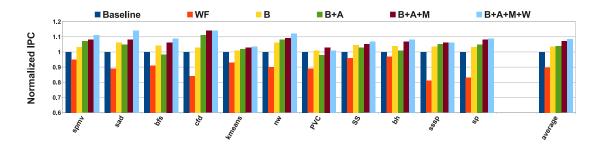

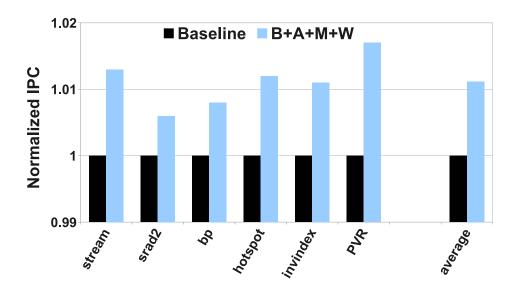

through a DRAM bank-aware shortest-job-first policy (BASJF, Section 4.3.3). We then augment it to be implicitly multicontroller aware (BASJF-AB, Section 4.3.4) by introducing an age bias in the scheduling scheme. We then further optimize the scheduler to regain the lost bandwidth utilization by carefully orchestrating the scheduling of row-miss requests (MERB, Section 4.3.5.1). We then couple this scheduler with a write-drain mechanism that reduces write-induced stall times for warps (WAWD, Section 4.3.6). The combined techniques reduce the adverse effects of memory divergence, reduce intrawarp latency variation, and thus improve performance by 8.6% on average.

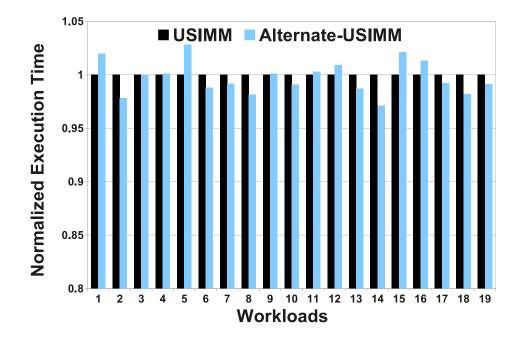

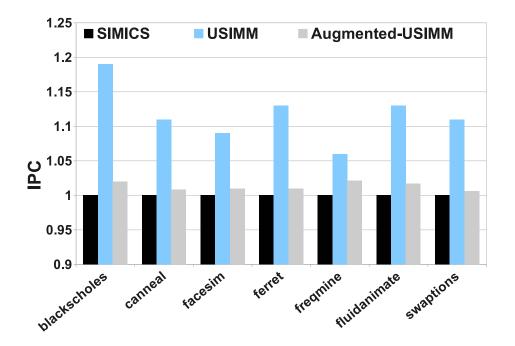

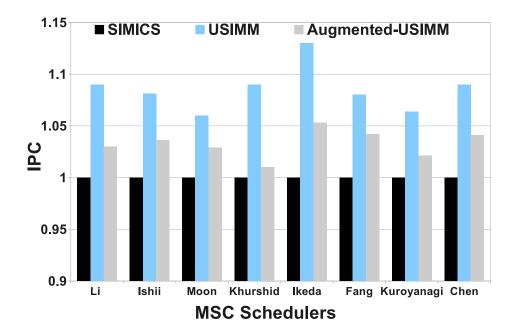

#### 1.2.4 Utah Simulated Memory Module

The Utah Simulated Memory Module (USIMM) was developed as the simulation framework for the 3rd Journal of Instruction Level Parallelism' Computer Architecture Competition: the Memory Scheduling Championship [20]. The tool has the potential to accelerate memory system research by the community. The dissertation discusses the design of the tool, analyzes its accuracy, and identifies important areas of focus for memory system research.

## CHAPTER 2

## BACKGROUND

In this section, we briefly look at the architecture of a modern memory system, the general features of modern memory schedulers, and the DRAM access characteristics of a graphics processing unit. This helps provide a background for the subsequent discussions where we investigate memory scheduling techniques that are aware of the internal characteristics of memory devices as well as the different access patterns generated by the clients of the memory system.

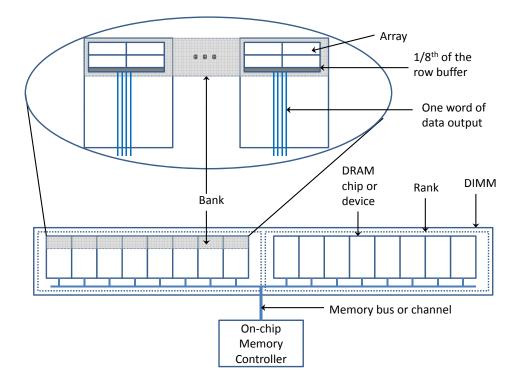

# 2.1 Memory System Basics2.1.1 DRAM System Organization