## Lecture 22: Cache Examples

- Today's topics:

- Cache access

- Example problems in cache design

# Accessing the Cache

## Accessing the Cache

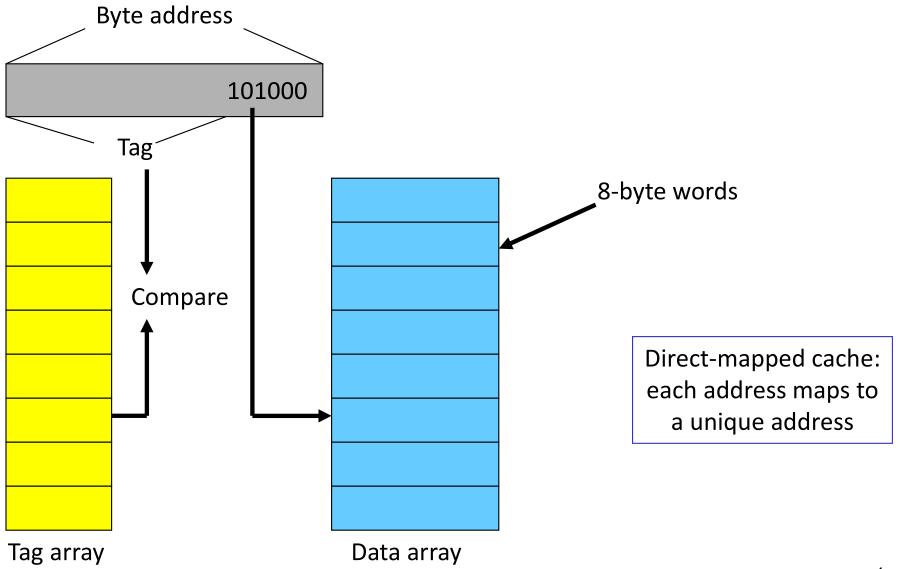

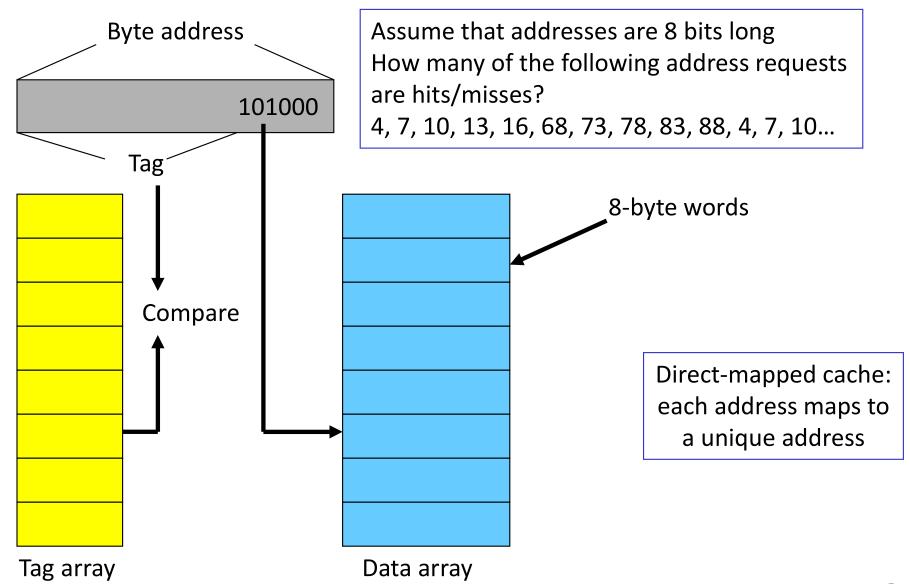

## The Tag Array

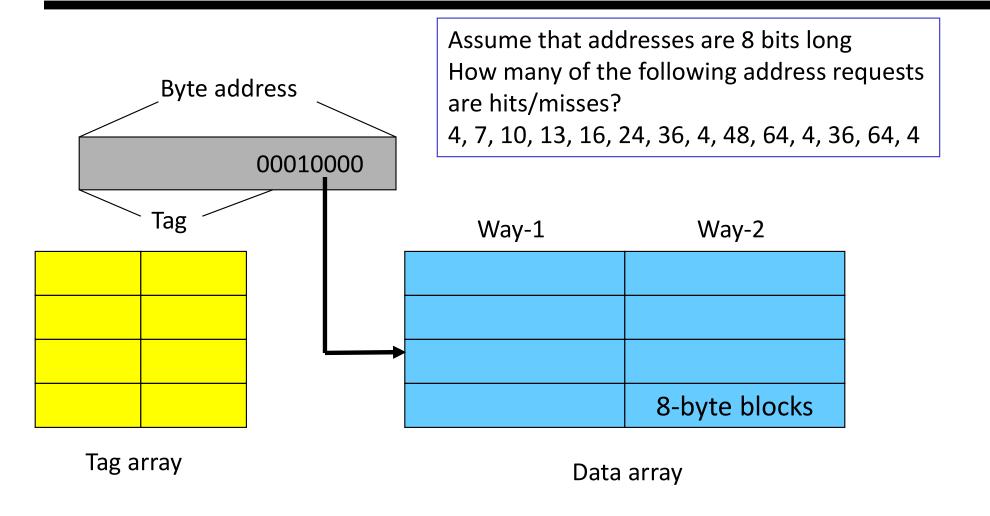

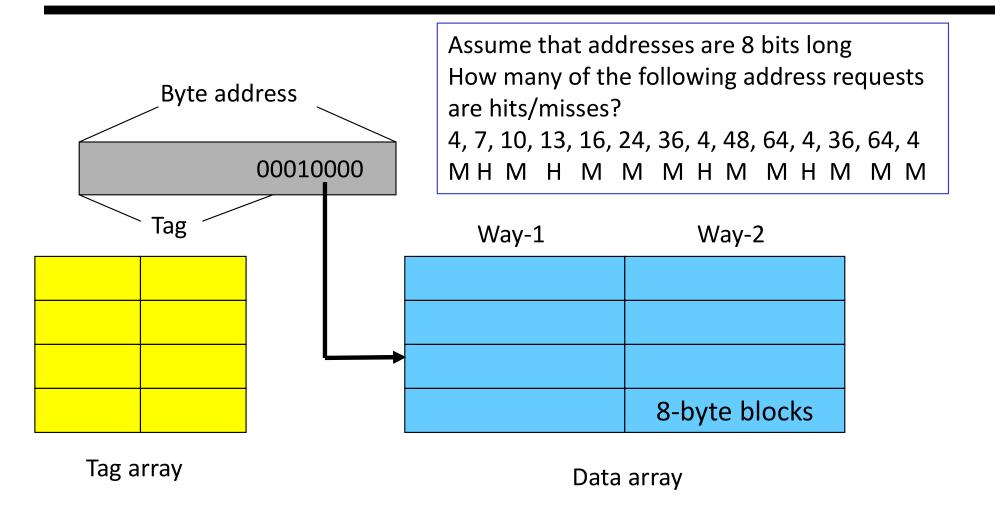

#### **Example Access Pattern**

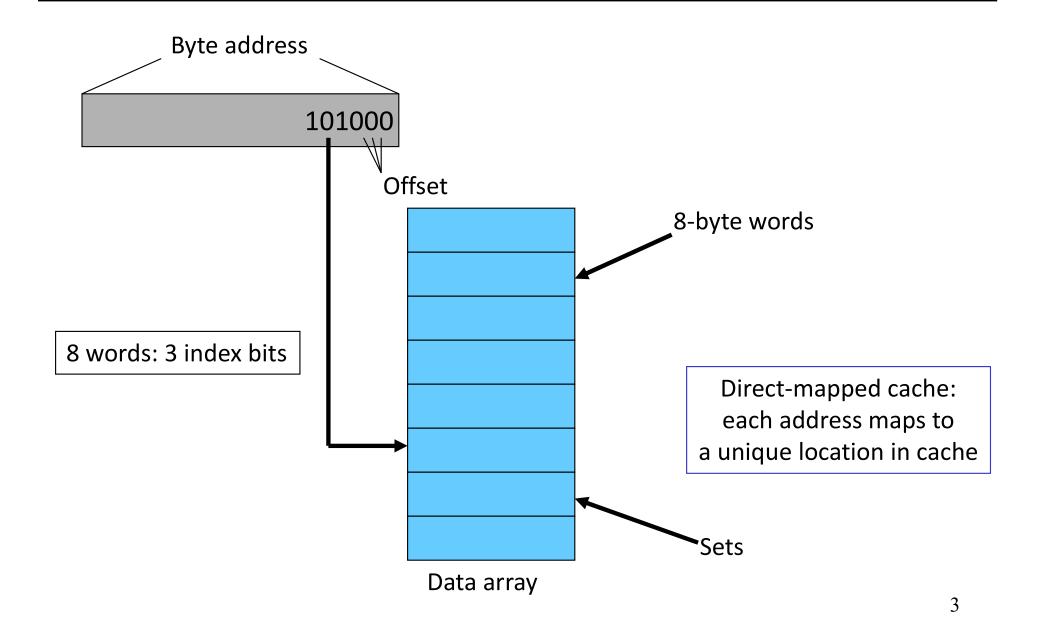

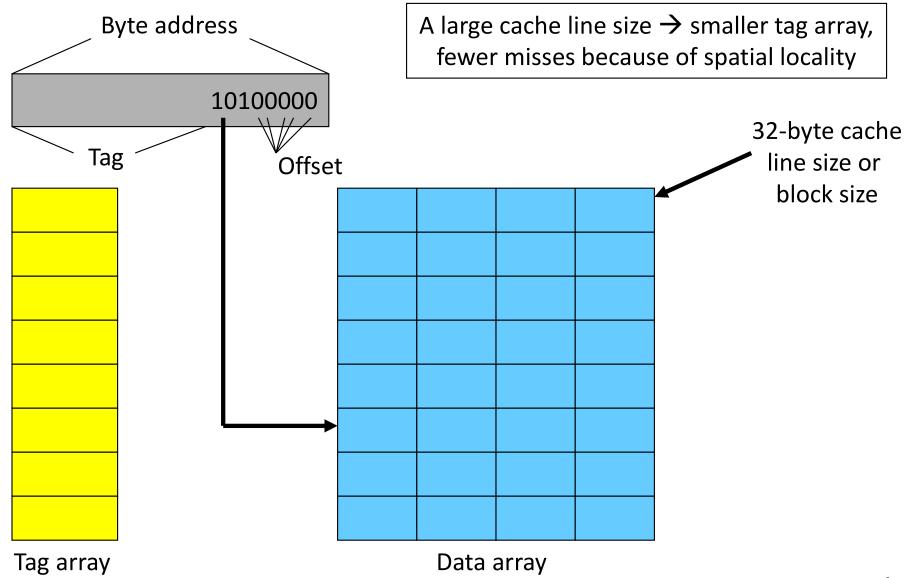

## **Increasing Line Size**

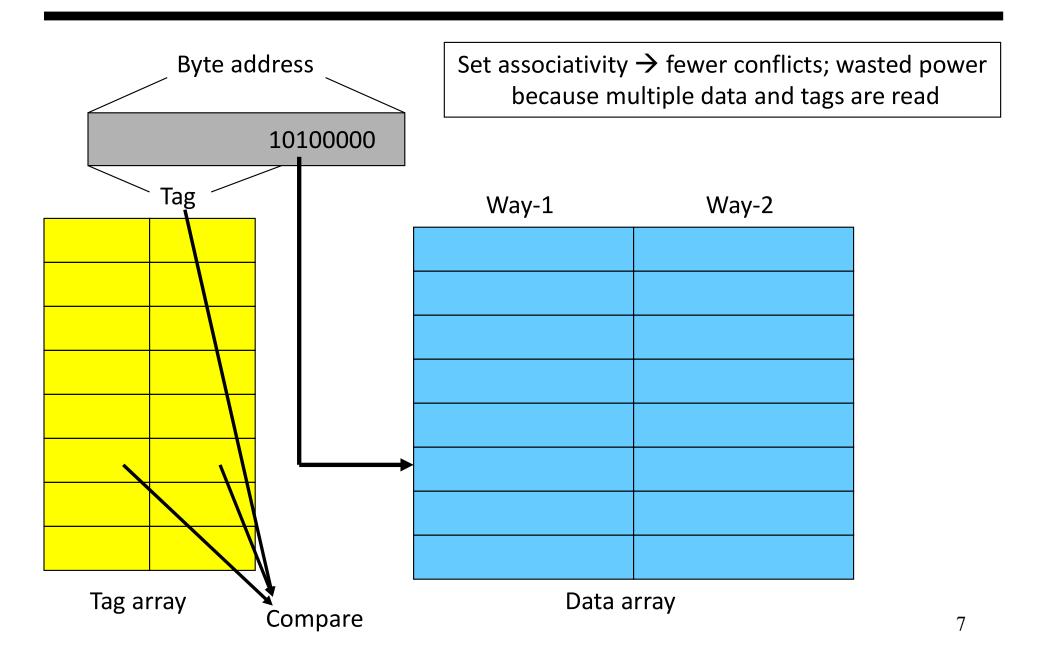

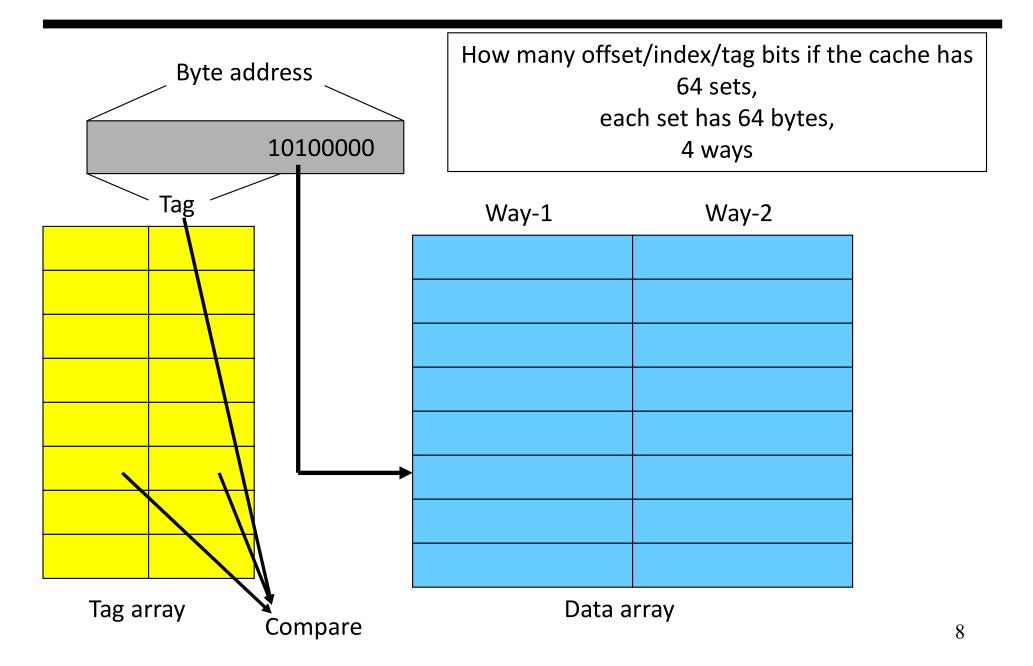

#### Associativity

#### Associativity

- 32 KB 4-way set-associative data cache array with 32 byte line sizes

- How many sets?

- How many index bits, offset bits, tag bits?

- How large is the tag array?

```

Cache size = #sets x #ways x blocksize

Index bits = log<sub>2</sub>(sets)

Offset bits = log<sub>2</sub>(blocksize)

Addr width = tag + index + offset

```

32 KB 4-way set-associative data cache array with 32 byte line sizes

cache size = #sets x #ways x block size

- How many sets? 256

- How many index bits, offset bits, tag bits?

8 5 19  $log_2(sets)$   $log_2(blksize)$  addrsize-index-offset

How large is the tag array?

tag array size = #sets x #ways x tag size

= 19 Kb = 2.375 KB

Show how the following addresses map to the cache and yield hits or misses. The cache is direct-mapped, has 16 sets, and a 64-byte block size.

Addresses: 8, 96, 32, 480, 976, 1040, 1096

Offset = address % 64 (address modulo 64, extract last 6) Index = address/64 % 16 (shift right by 6, extract last 4) Tag = address/1024 (shift address right by 10)

| • |  |

|---|--|

| • |  |

| • |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|      |             | 32-bit address |               |   |

|------|-------------|----------------|---------------|---|

|      | 22 bits tag | 4 bits index   | 6 bits offset |   |

| 8:   | 0           | 0              | 8             | M |

| 96:  | 0           | 1              | 32            | M |

| 32:  | 0           | 0              | 32            | Н |

| 480: | 0           | 7              | 32            | M |

| 976: | 0           | 15             | 16            | M |

| 1040 | : 1         | 0              | 16            | M |

| 1096 | 1           | 1              | 8             | M |

A pipeline has CPI 1 if all loads/stores are L1 cache hits 40% of all instructions are loads/stores

85% of all loads/stores hit in 1-cycle L1

50% of all (10-cycle) L2 accesses are misses

Memory access takes 100 cycles

What is the CPI?

A pipeline has CPI 1 if all loads/stores are L1 cache hits 40% of all instructions are loads/stores

85% of all loads/stores hit in 1-cycle L1

50% of all (10-cycle) L2 accesses are misses

Memory access takes 100 cycles

What is the CPI?

```

Start with 1000 instructions

1000 cycles (includes all 400 L1 accesses)

+ 400 (ld/st) x 15% x 10 cycles (the L2 accesses)

+ 400 x 15% x 50% x 100 cycles (the mem accesses)

= 4,600 cycles

CPI = 4.6

```