# Lecture 14: Sequential Circuits, FSM

• Today's topics:

Combinational Ccts

- Adder wrap-up

- Sequential circuits

- Finite state machines

addi \$t3, \$t3, 100

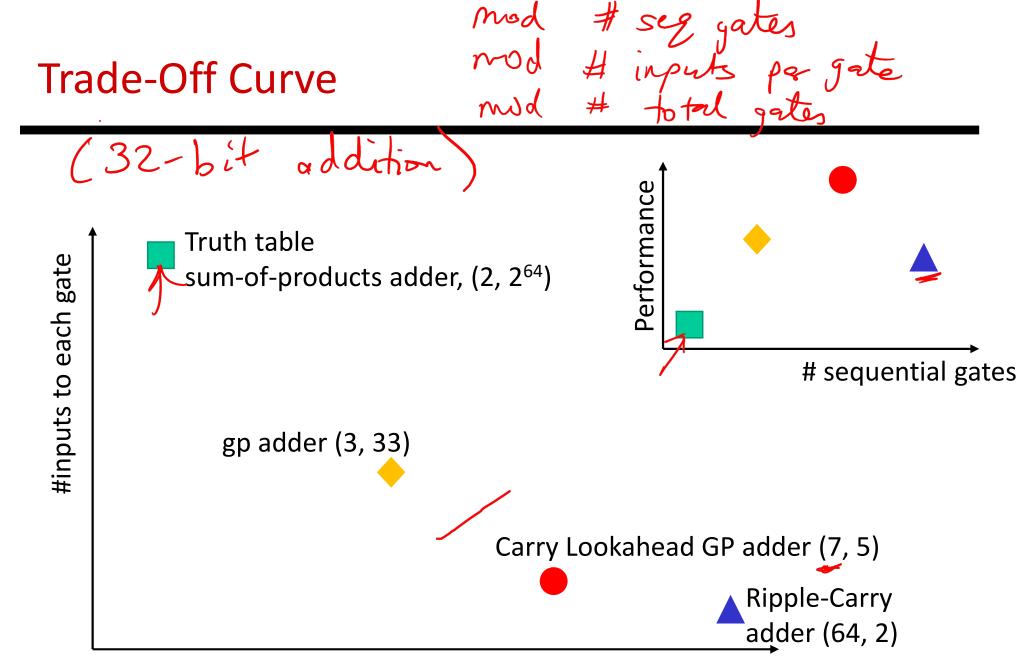

## **Adder Summary**

- Using the generate/propagate abstraction to add layers of ccts

- Key: all g/p/G/P signals can be calculated based on a/b inputs

(they don't need carry-in as inputs, so they can all be done rightaway in parallel)

- First calculate g/p with 1 gate delay: gi = ai.bi ; pi = ai + bi

- Then calculate G/P with up to 2 gate delays (for a block of 4 bits):

Gi =

$$g3 + g2.p3 + g1.p2.p3 + g0.p1.p2.p3$$

Pi =  $p0.p1.p2.p3$

Then calculate all the carries, including for the 16<sup>th</sup> bit, with 2 more gate delays:

$$C4 = G3 + (P3.G2) + (P3.P2.G1) + (P3.P2.P1.G0) + (P3.P2.P1.P0.c0)$$

Thus, this abstraction enables a design with a modest number of total gates, a modest number of delays, and a modest number of inputs per gate.

# sequential gates

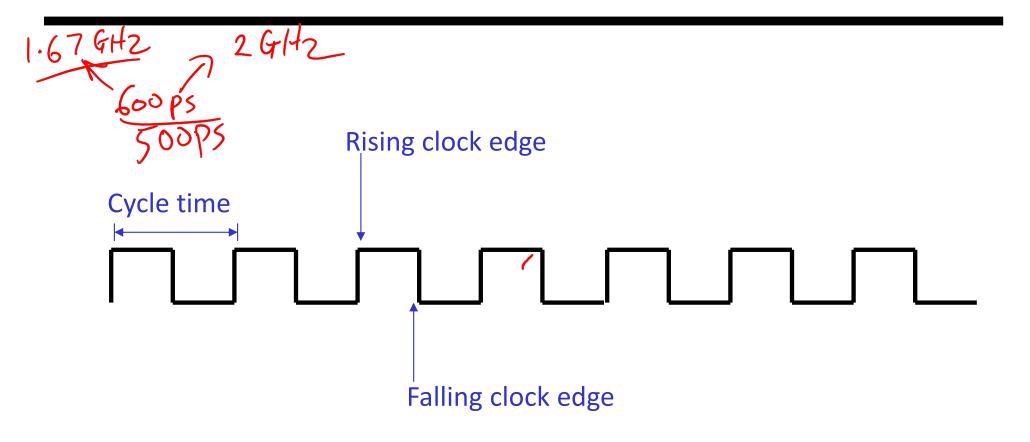

#### Clocks

- A microprocessor is composed of many different circuits that are operating simultaneously if each circuit X takes in inputs at time  $TI_X$ , takes time  $TE_X$  to execute the logic, and produces outputs at time  $TO_X$ , imagine the complications in co-ordinating the tasks of every circuit

- A major school of thought (used in most processors built today): all circuits on the chip share a clock signal (a square wave) that tells every circuit when to accept inputs, how much time they have to execute the logic, and when they must produce outputs

## **Clock Terminology**

$$4 \text{ GHz} = \text{clock speed} = \underbrace{1}_{\text{cycle time}} = \underbrace{1}_{\text{cycle time}}.$$

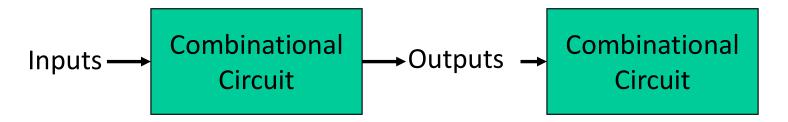

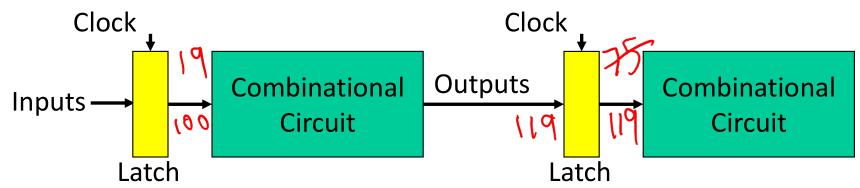

## **Sequential Circuits**

Until now, circuits were combinational – when inputs change, the outputs change after a while (time = logic delay thru circuit)

We want the clock to act like a start and stop signal – a "latch" is a storage device that separates these circuits – it ensures that the inputs to the circuit do not change during a clock cycle

## Sequential Circuits

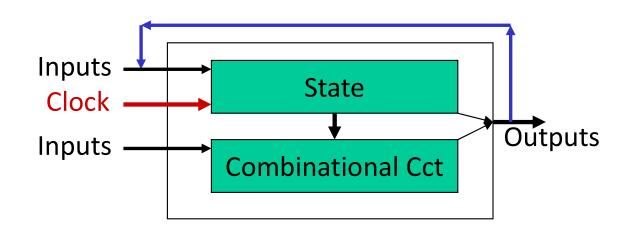

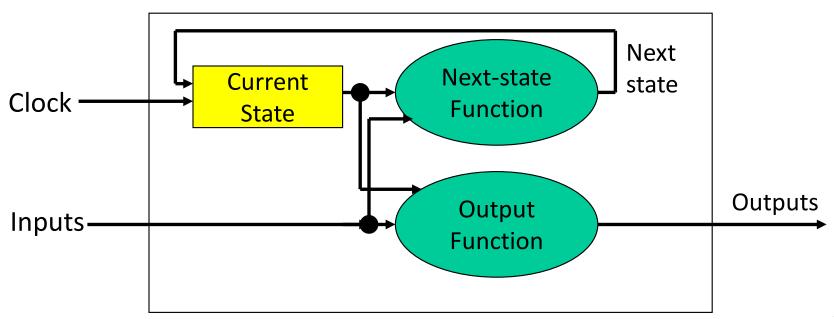

- Sequential circuit: consists of combinational circuit and a storage element

- At the start of the clock cycle, the rising edge causes the "state" storage to store some input values

- This state will not change for an entire cycle (until next rising edge)

- The combinational circuit has some time to accept the value of "state" and "inputs" and produce "outputs"

- Some of the outputs (for example, the value of next "state") may feed back (but through the latch so they're only seen in the next cycle)

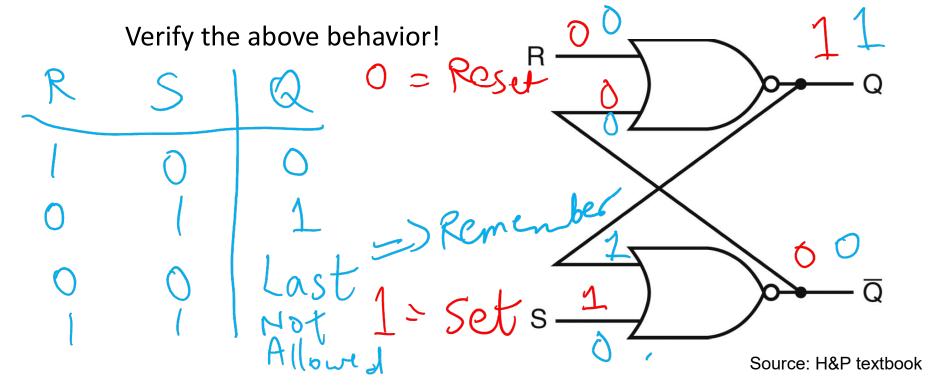

# Designing a Latch

- An S-R latch: set-reset latch

- When Set is high, a 1 is stored

- When Reset is high, a 0 is stored

- When both are low, the previous state is preserved (hence, known as a storage or memory element)

- Both are high this set of inputs is not allowed

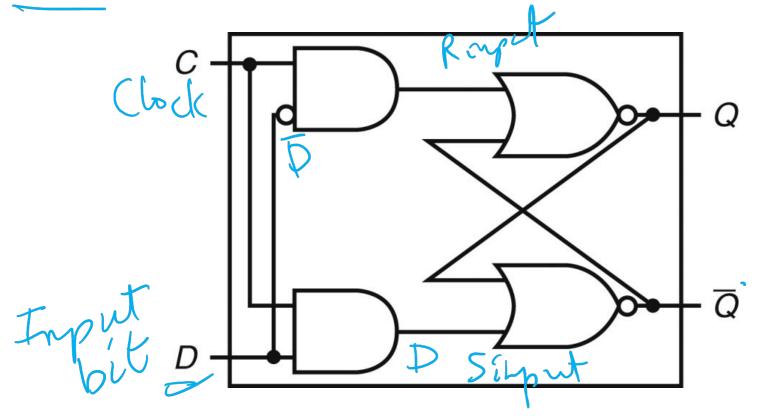

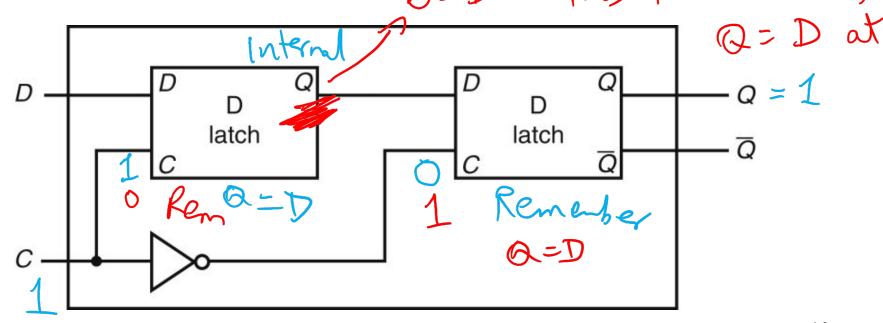

### D Latch

clockis

remember state

Incorporates a clock

The value of the input D signal (data) is stored only when the clock is high – the previous state is preserved when the clock is low

Q=D

# D Flip Flop

Snaps at ever  $\alpha = 1$  erminology:

Latch: outputs can change any time the clock is high (asserted)

Flip flop: outputs can change only on a clock edge

• Two D latches in series – ensures that a value is stored only on the falling edge of the clock

10

#### Finite State Machine

- A sequential circuit is described by a variation of a truth table – a finite state diagram (hence, the circuit is also called a finite state machine)

- Note that state is updated only on a clock edge

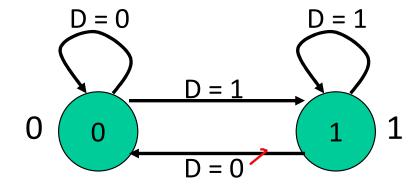

# **State Diagrams**

curistate Doubput state

0 0 0

1 1

1

Each state is shown with a circle, labeled with the state value – the contents of the circle are the outputs clk exists

An arc represents a transition to a different state, with the inputs indicated on the label

saturating

Counter

2 output states 0 + 1

This is a state diagram for \_\_\_\_?

1 input D with 2 values 0 & 1<sup>12</sup>

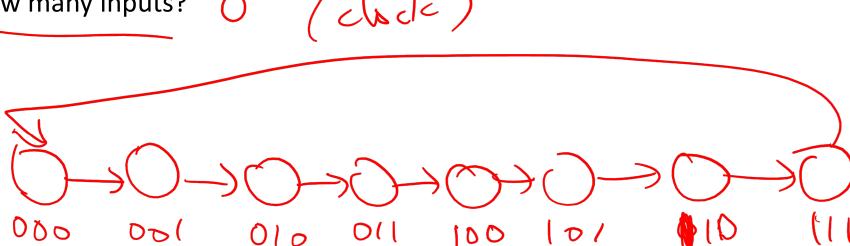

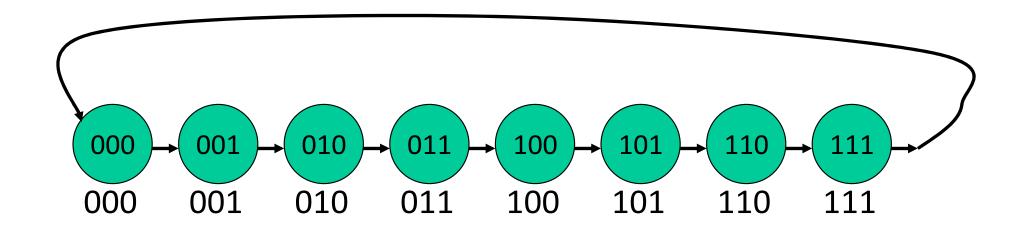

## 3-Bit Counter

Consider a circuit that stores a number and increments the value on every clock edge – on reaching the largest value, it starts again from 0

Draw the state diagram:

- How many states?

- How many inputs?

#### 3-Bit Counter

Consider a circuit that stores a number and increments the value on every clock edge – on reaching the largest value, it starts again from 0

Draw the state diagram:

- How many states?

- How many inputs?

## Tackling FSM Problems

- Three questions worth asking:

- What are the possible output states? Draw a bubble for each.

- What are inputs? What values can those inputs take?

- For each state, what do I do for each possible input value? Draw an arc out of every bubble for every input value.

# Traffic Light Controller

Problem description: A traffic light with only green and red; either the North-South road has green or the East-West road has green (both can't be red); there are detectors on the roads to indicate if a car is on the road; the lights are updated every 30 seconds; a light need change only if a car is waiting on the other road

**State Transition Table:**

How many states?

How many inputs?

How many outputs?

Well or Modification Table:

Modificat

2 Sersoss

#### **State Transition Table**

Problem description: A traffic light with only green and red; either the North-South road has green or the East-West road has green (both can't be red); there are detectors on the roads to indicate if a car is on the road; the lights are updated every 30 seconds; a light must change only if a car is waiting on the other road

#### **State Transition Table:**

| CurrState | InputEW | InputNS | NextState=Output |

|-----------|---------|---------|------------------|

| N         | 0       | 0       | N                |

| N         | 0       | 1       | N                |

| N         | 1       | 0       | E                |

| N         | 1       | 1       | E                |

| Е         | 0       | 0       | Е                |

| Е         | 0       | 1       | Ν                |

| Е         | 1       | 0       | Е                |

| Е         | 1       | 1       | Ν                |

# State Diagram

#### **State Transition Table:**

| race manistric             | on labic. |         |                  |  |  |  |

|----------------------------|-----------|---------|------------------|--|--|--|

| CurrState                  | InputEW   | InputNS | NextState=Output |  |  |  |

| N                          | 0         | 0       | N                |  |  |  |

| Ν                          | 0         | 1       | N                |  |  |  |

| Ν                          | 1         | 0       | E                |  |  |  |

| Ν                          | 1         | 1       | E                |  |  |  |

| Е                          | 0         | 0       | Е                |  |  |  |

| Е                          | 0         | 1       | N                |  |  |  |

| Е                          | 1         | 0       | Е                |  |  |  |

| Е                          | 1         | 1       | N                |  |  |  |

|                            |           | EWcar   |                  |  |  |  |

|                            |           |         |                  |  |  |  |

| NSgreen NScar EWlite EWcar |           |         |                  |  |  |  |

Source: H&P textbook