# Lecture 1: CS/ECE 3810 Introduction

- Today's topics:

- Why computer organization is important

- Logistics

- Modern trends

Image credits: uber, extremetech, anandtech

- Efficiency is important! You learn about big-O notation in Algorithms, you learn about the constants in this class

- The AI revolution owes a lot to fast hardware; a complete CS/CE education includes a deep understanding of hardware

- Embarrassing if you are a BS in CS/CE and can't make sense of the following terms: DRAM, pipelining, cache hierarchies, I/O, virtual memory, ...

- Embarrassing if you are a BS in CS/CE and can't decide which processor to buy: 4.4 GHz Intel Core i9 or 4.7 GHz AMD Ryzen 7 (reason about performance/power)

- Obvious first step for chip designers, compiler/OS writers

- Will knowledge of the hardware help you write better and more secure programs?

## Must a Programmer Care About Hardware?

- Must know how to reason about program performance and energy and security

- Memory management: if we understand how/where data is placed, we can help ensure that relevant data is nearby

- Thread management: if we understand how threads interact, we can write smarter multi-threaded programs

- $\rightarrow$  Why do we care about multi-threaded programs?

200x speedup for matrix vector multiplication

- Data level parallelism: 3.8x

- Loop unrolling and out-of-order execution: 2.3x

- Cache blocking: 2.5x

- Thread level parallelism: 14x

Further, can use accelerators to get an additional 100x.

## **Key Topics**

- Moore's Law, power wall

- Use of abstractions

- Assembly language

- Computer arithmetic

- Pipelining

- Using predictions

- Memory hierarchies

- Accelerators

- Reliability and Security

#### Logistics

- See class web-page for syllabus/resources https://www.cs.utah.edu/~rajeev/cs3810

- TAs and office hours: on the class webpage

- Most communication on Canvas and Piazza; email me directly to set up meetings, or meet me in office hours right before class

- Textbook: Computer Organization HW/SW Interface, Patterson and Hennessy, 5<sup>th</sup> or 6<sup>th</sup> edition

#### **Course Organization**

- 40% two midterms, 40% final, 20% assignments

- ~10 assignments you may skip two; automatic 1.5 day extension until Wed/Fri late night; upload on Gradescope; HW4 has extra credit

- Co-operation policy: you may discuss you may not see someone else's written matter when writing your solution

- Exams are open-notes (1 page)

- Print slides just before class

- Screencast YouTube videos

# **Grading Policy**

- Grading by rank (32% receive A or A-, 40% receive B+/B/B-)

- About 13% receive D+ or lower

- No tolerance for cheating (see class webpage)

- Rank in exams matters more than rank in homeworks

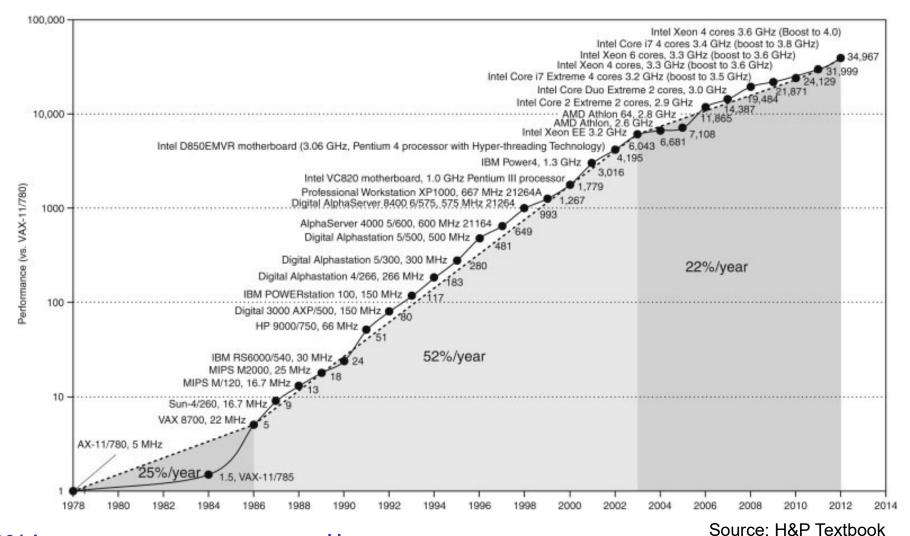

## **Microprocessor Performance**

50% improvement every year!! What contributes to this improvement? Why the lower improvement?

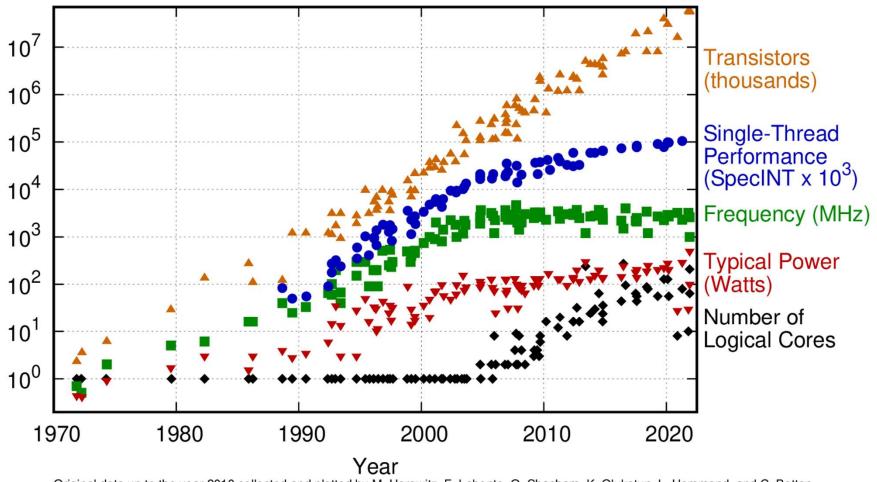

### **Transistors and Clocks**

- Basic device used to create logic gates, circuits

- Smaller transistors → more circuits, faster circuits

- Clock: a voltage signal that goes up and down, serving as a start/stop signal for circuits; 4 GHz clock frequency = 4 billion up/downs in a second

## **Microprocessor Performance**

50 Years of Microprocessor Trend Data

Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten New plot and data collected for 2010-2021 by K. Rupp

Source: karlrupp.net

<sup>14</sup>

## **Microprocessor Performance**

| Processor<br>branding | Model 🗢   | Cores<br>(threads) |            | Clock rate (GHz) |            |             |            |         |      | GPU        |         |         |        |         |                        |

|-----------------------|-----------|--------------------|------------|------------------|------------|-------------|------------|---------|------|------------|---------|---------|--------|---------|------------------------|

|                       |           |                    |            | Base             |            | Turbo Boost |            |         |      |            | Max.    | Smart 🖕 | TDP    |         | Price                  |

|                       |           |                    |            |                  |            | 2.0         |            | 3.0 TVB |      | Model +    | freq. 🕈 |         |        |         | (USD) <sup>[a]</sup> ◆ |

|                       |           | <u>P</u> +         | <u>E</u> + | <u>P</u> +       | <u>E</u> + | <u>P</u> +  | <u>E</u> + | P ¢     | P \$ |            | (GHz)   |         | Base + | Turbo 🕈 |                        |

| Core i9               | 14900KS 🖉 | -                  | 16<br>(16) | 3.2              | 2.4        | 5.7         | 4.5        | 5.9     | 6.2  | UHD        | 1.65    | 36 MB   | 150 W  | 253 W   | \$689                  |

|                       | 14900K 🖄  |                    |            |                  |            | 5.6         | 4.4        | 5.8     | 6.0  | 770        | 1.00    |         | 125 W  |         | \$589                  |

|                       | 14900KF 🛃 |                    |            |                  |            |             |            |         |      | N          | /A      |         |        |         | \$564                  |

|                       | 14900 亿   |                    |            | 2.0              | 1.5        | 5.4         | 4.3        | 5.6     | 5.8  | UHD<br>770 | 1.65    |         | 65 W   | 219 W   | \$549                  |

|                       | 14900F 🖉  |                    |            |                  |            |             |            |         |      | N          | N/A     |         |        |         | \$524                  |

|                       | 14900T 년  | 8                  |            | 1.1              | 0.8        | 5.1         | 4.0        | 5.5     |      | UHD<br>770 | 1.65    | -       | 35 W   | 106 W   | \$549                  |

|                       | 14790F 🗗  | 8<br>(16)          | 8<br>(8)   | 2.1              | 1.5        | 5.3         | 4.2        | 5.4     |      | N          | /Α      |         | 65 W   | 219 W   | China<br>only          |

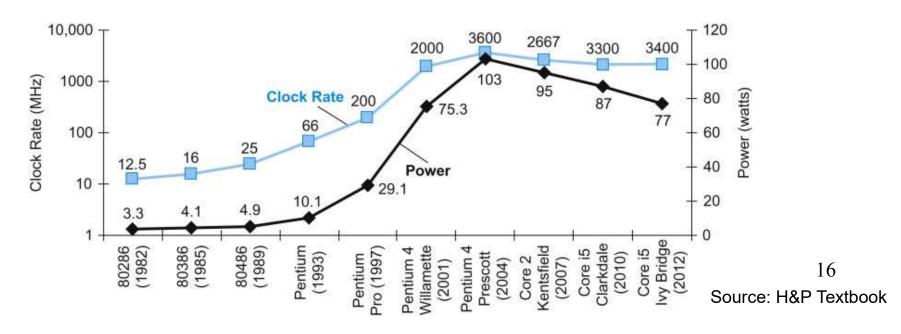

#### **Power Consumption Trends**

- Dyn power  $\alpha$  activity x capacitance x voltage<sup>2</sup> x frequency

- Voltage and frequency are somewhat constant now, while capacitance per transistor is decreasing and number of transistors (activity) is increasing

- Leakage power is also rising (function of #trans and voltage)

- Running out of ideas to improve single thread performance

- Power wall makes it harder to add complex features

- Power wall makes it harder to increase frequency

- Technology scaling likely to end soon

- Additional performance provided by: more cores, occasional spikes in frequency, accelerators

- Three roadblocks: power, ideas, technology scaling

- Fixed power budget because of cooling constraints; implies that frequency can't be increased; discourages complex ideas

- End of voltage (Dennard) scaling in early 2010s; the end of Moore's Law also imminent

- Has led to dark silicon and dim silicon (occasional turbo)

- Topics: Trends, Performance, MIPS instruction set architecture (Chapter 2)

- Visit the class web-page https://www.cs.utah.edu/~rajeev/cs3810