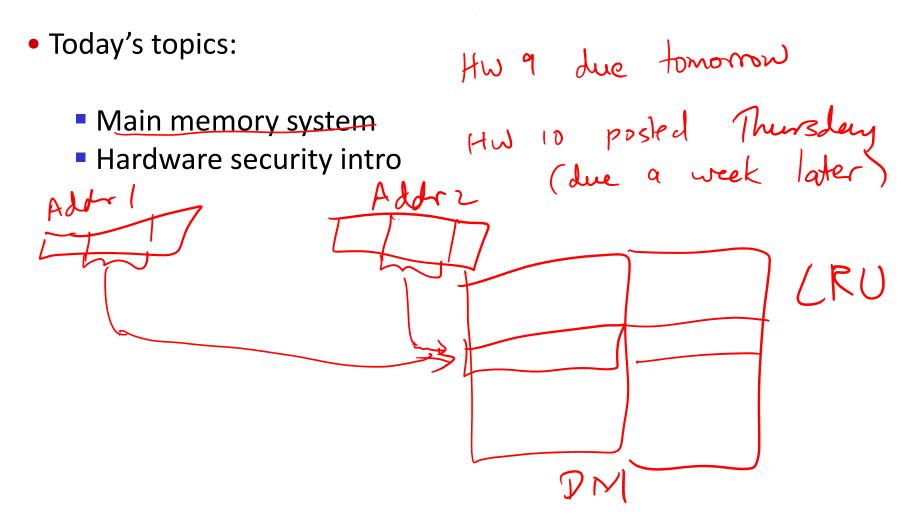

# Lecture 24: Memory, Security

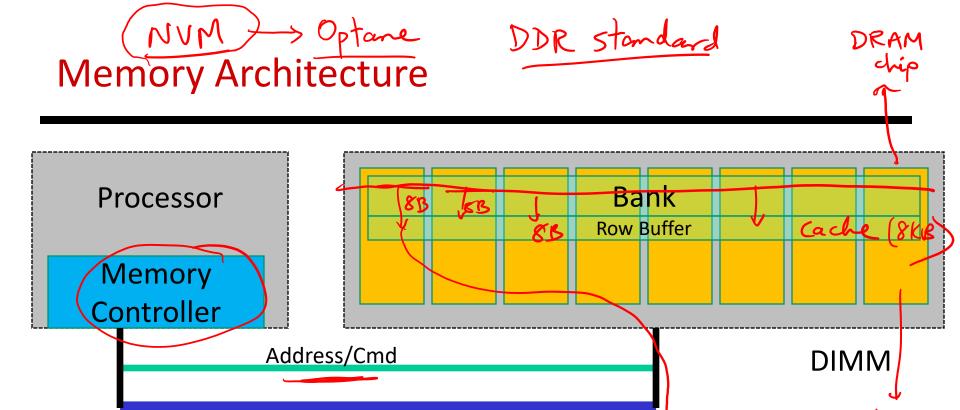

• Main memory is stored in DRAM cells that have much higher storage density

volatile

- DRAM cells lose their state over time must be refreshed periodically, hence the name *Dynamic*

- A number of DRAM chips are aggregated on a DIMM to provide high capacity – a DIMM is a module that plugs into a bus on the motherboard

- DRAM access suffers from long access time and high 8Gb DIM energy overhead 300 cycles = 1 GR

DIMM: a PCB with DRAM chips on the back and front

Data

- The memory system is itself organized into ranks and banks; each bank can process a transaction in parallel

- Each bank has a row buffer that retains the last row touched in a bank (it's like a cache in the memory system that exploits spatial locality) (row buffer hits have a lower latency than a row buffer miss)

bit

# **Hardware Security**

- Software security: key management, buffer overflow, etc.

- Hardware security: hardware-enforced permission checks, authentication/encryption, etc.

- Information leakage, side channels, timing channels

• Meltdown, Spectre, SGX

Threat Model

OS would be melicions

# Meltdown ia [4095] 9[82] Attacker serve ( (20 d) R3 Sef# 82

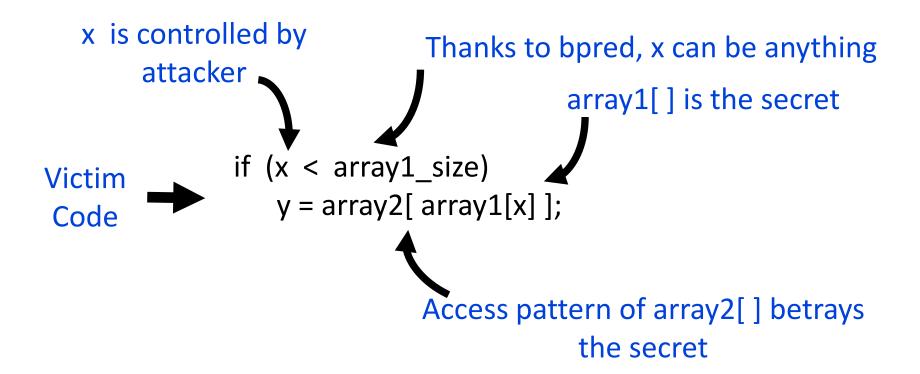

## Spectre: Variant 1

## Spectre: Variant 2

#### Attacker code

Label0: if (1)

Label1: ...

#### Victim code

R1 ← (from attacker)

R2 ← some secret

Label0: if (...)

### Victim code

Label1:

lw [R2]