### Lecture 12: Hardware for Arithmetic

- Today's topics:

- Logic for common operations

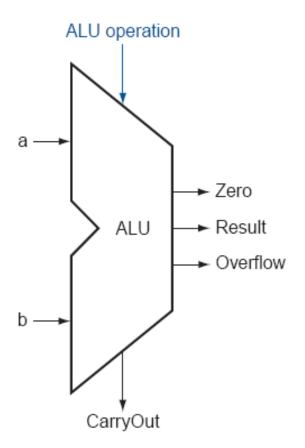

- Designing an ALU

# Logic Blocks

- A logic block has a number of binary inputs and produces a number of binary outputs – the simplest logic block is composed of a few transistors

- A logic block is termed combinational if the output is only a function of the inputs

- A logic block is termed sequential if the block has some internal memory (state) that also influences the output

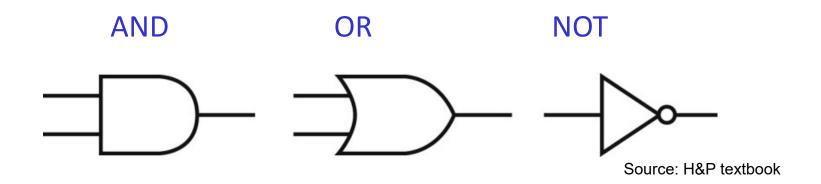

- A basic logic block is termed a gate (AND, OR, NOT, etc.)

- We will only deal with combinational circuits today

### Truth Table

- A truth table defines the outputs of a logic block for each set of inputs

- Consider a block with 3 inputs A, B, C and an output E that is true only if exactly 2 inputs are true

| _ | Α | В | С | Е |

|---|---|---|---|---|

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

|   |   |   |   |   |

### Truth Table

- A truth table defines the outputs of a logic block for each set of inputs

- Consider a block with 3 inputs A, B, C and an output E that is true only if exactly 2 inputs are true

| Α | В | C | Е |                           |

|---|---|---|---|---------------------------|

| 0 | 0 | 0 | 0 |                           |

| 0 | 0 | 1 | 0 |                           |

| 0 | 1 | 0 | 0 |                           |

| 0 | 1 | 1 | 1 |                           |

| 1 | 0 | 0 | 0 | Can be compressed by only |

| 1 | 0 | 1 | 1 | representing cases that   |

| 1 | 1 | 0 | 1 | have an output of 1       |

| 1 | 1 | 1 | 0 | ,                         |

|   |   |   |   |                           |

## **Boolean Algebra**

- Equations involving two values and three primary operators:

- OR: symbol + , X = A + B → X is true if at least one of A or B is true

- AND : symbol . , X = A . B → X is true if both A and B are true

- NOT : symbol ,  $X = A \rightarrow X$  is the inverted value of A

## Boolean Algebra Rules

- Identity law : A + 0 = A ; A . 1 = A

- Zero and One laws: A + 1 = 1; A.0 = 0

- Inverse laws : A . A = 0 ; A + A = 1

- Commutative laws: A + B = B + A ; A . B = B . A

- Associative laws: A + (B + C) = (A + B) + C

A . (B . C) = (A . B) . C

- Distributive laws : A . (B + C) = (A . B) + (A . C)

A + (B . C) = (A + B) . (A + C)

# DeMorgan's Laws

$$\bullet \overline{A + B} = \overline{A} \cdot \overline{B}$$

$$\bullet \ A . B = A + B$$

Confirm that these are indeed true

# **Pictorial Representations**

### What logic function is this?

ource. Har textbook

## **Boolean Equation**

Consider the logic block that has an output E that is true only if exactly two of the three inputs A, B, C are true

Multiple correct equations:

Two must be true, but all three cannot be true:

$$E = ((A . B) + (B . C) + (A . C)) . (A . B . C)$$

Identify the three cases where it is true:

$$E = (A . B . \overline{C}) + (A . C . \overline{B}) + (C . B . \overline{A})$$

#### Sum of Products

- Can represent any logic block with the AND, OR, NOT operators

- Draw the truth table

- For each true output, represent the corresponding inputs as a product

- The final equation is a sum of these products

| Α | В | C | Е |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

$$(A . B . \overline{C}) + (A . C . \overline{B}) + (C . B . \overline{A})$$

- Can also use "product of sums"

- Any equation can be implemented with an array of ANDs, followed by an array of ORs

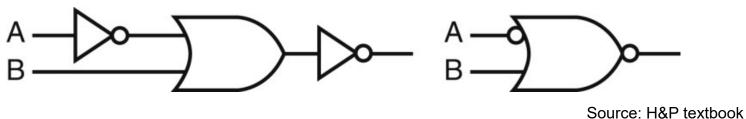

#### NAND and NOR

- NAND: NOT of AND: A nand B = A.B

- NOR: NOT of OR: A nor B = A + B

- NAND and NOR are *universal gates*, i.e., they can be used to construct any complex logical function

# Common Logic Blocks – Decoder

Takes in N inputs and activates one of 2<sup>N</sup> outputs

| I <sub>0</sub> | I <sub>1</sub>                     | I <sub>2</sub> |  | <b>O</b> <sub>0</sub> | 01 | 02 | O <sub>3</sub> | O <sub>4</sub> | <b>O</b> <sub>5</sub> | <b>O</b> <sub>6</sub> | O <sub>7</sub> |

|----------------|------------------------------------|----------------|--|-----------------------|----|----|----------------|----------------|-----------------------|-----------------------|----------------|

| 0              | 0                                  | 0              |  | 1                     | 0  | 0  | 0              | 0              | 0                     | 0                     | 0              |

| 0              | 0                                  | 1              |  | 0                     | 1  | 0  | 0              | 0              | 0                     | 0                     | 0              |

| 0              | 1                                  | 0              |  | 0                     | 0  | 1  | 0              | 0              | 0                     | 0                     | 0              |

| 0              | 1                                  | 1              |  | 0                     | 0  | 0  | 1              | 0              | 0                     | 0                     | 0              |

| 1              | 0                                  | 0              |  | 0                     | 0  | 0  | 0              | 1              | 0                     | 0                     | 0              |

| 1              | 0                                  | 1              |  | 0                     | 0  | 0  | 0              | 0              | 1                     | 0                     | 0              |

| 1              | 1                                  | 0              |  | 0                     | 0  | 0  | 0              | 0              | 0                     | 1                     | 0              |

| 1              | 1                                  | 1              |  | 0                     | 0  | 0  | 0              | 0              | 0                     | 0                     | 1              |

|                | 3-to-8<br>Decoder O <sub>0-7</sub> |                |  |                       |    |    |                |                |                       |                       |                |

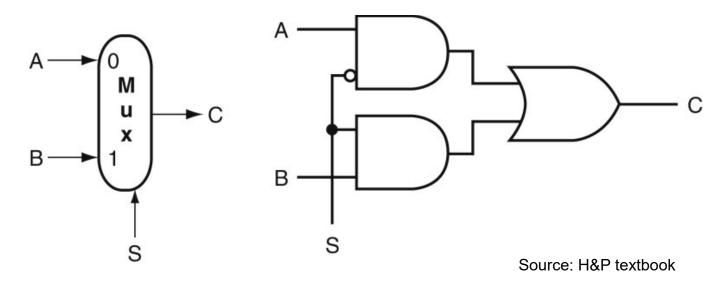

# Common Logic Blocks – Multiplexor

Multiplexor or selector: one of N inputs is reflected on the output depending on the value of the log<sub>2</sub>N selector bits

2-input mux

# Adder Algorithm

#### Truth Table for the above operations:

| A | В | Cin | Sum Cout |

|---|---|-----|----------|

| 0 | 0 | 0   |          |

| 0 | 0 | 1   |          |

| 0 | 1 | 0   |          |

| 0 | 1 | 1   |          |

| 1 | 0 | 0   |          |

| 1 | 0 | 1   |          |

| 1 | 1 | 0   |          |

| 1 | 1 | 1   |          |

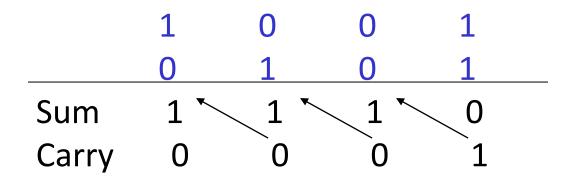

## Adder Algorithm

|       | 1 | 0 | 0 | 1 |  |

|-------|---|---|---|---|--|

|       | 0 | 1 | 0 | 1 |  |

| Sum   | 1 | 1 | 1 | 0 |  |

| Carry | 0 | 0 | Ô | 1 |  |

#### Truth Table for the above operations:

| В | Cin                                       | Sum Cout                                     |

|---|-------------------------------------------|----------------------------------------------|

| 0 | 0                                         | 0 0                                          |

| 0 | 1                                         | 1 0                                          |

| 1 | 0                                         | 1 0                                          |

| 1 | 1                                         | 0 1                                          |

| 0 | 0                                         | 1 0                                          |

| 0 | 1                                         | 0 1                                          |

| 1 | 0                                         | 0 1                                          |

| 1 | 1                                         | 1 1                                          |

|   | B<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | B Cin  0 0 0 1 1 0 1 1 0 0 0 1 1 1 0 1 1 1 1 |

#### **Equations:**

Sum = Cin

$$.\overline{A} .\overline{B} + B .\overline{Cin} .\overline{A} + A .\overline{Cin} .\overline{B} + A .B .Cin$$

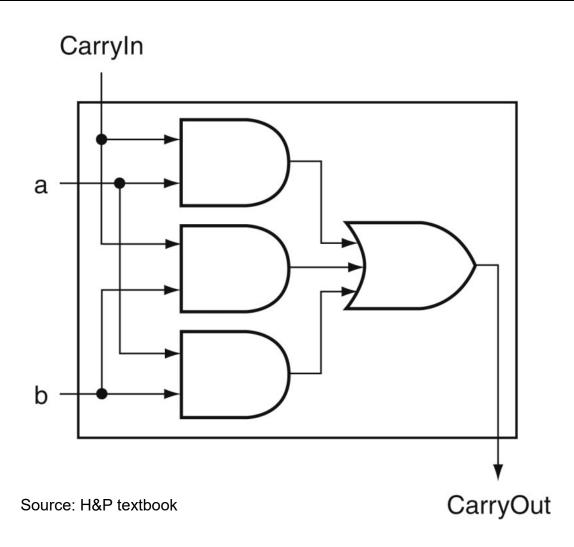

# **Carry Out Logic**

#### **Equations:**

Sum = Cin

$$.\overline{A} .\overline{B} + B .Cin .\overline{A} + A .Cin .\overline{B} + A .B .Cin$$

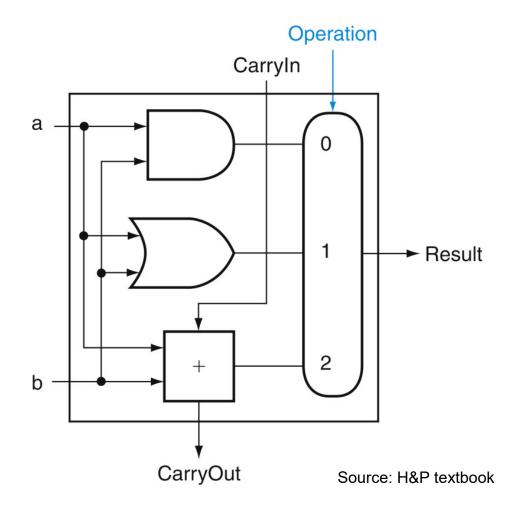

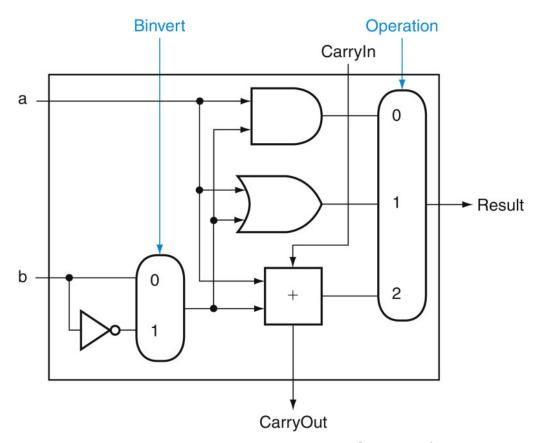

## 1-Bit ALU with Add, Or, And

Multiplexor selects between Add, Or, And operations

17

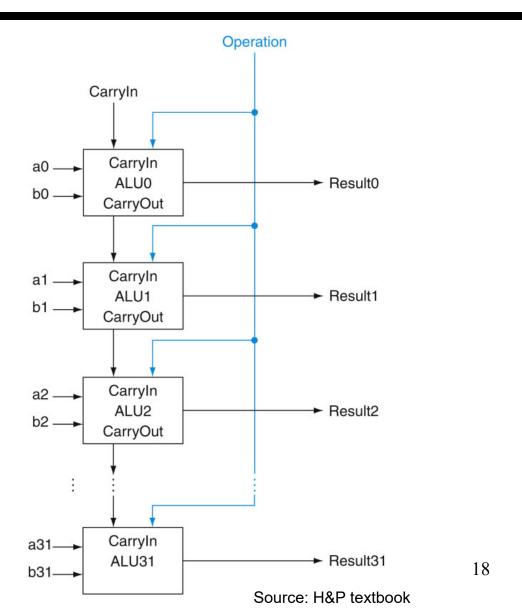

# 32-bit Ripple Carry Adder

1-bit ALUs are connected "in series" with the carry-out of 1 box going into the carry-in of the next box

### **Incorporating Subtraction**

#### Must invert bits of B and add a 1

- Include an inverter

- CarryIn for the first bit is 1

- The CarryIn signal (for the first bit) can be the same as the Binvert signal

Source: H&P textbook

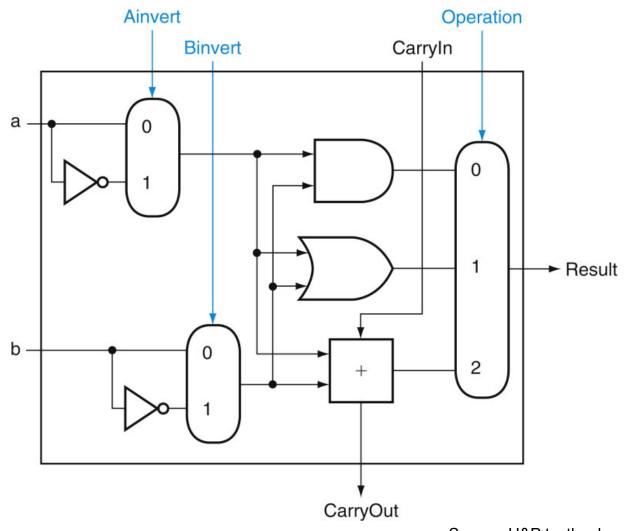

# **Incorporating NOR and NAND**

Source: H&P textbook

### **Control Lines**

What are the values of the control lines and what operations do they correspond to?

|      | Ai | Bn | Op |

|------|----|----|----|

| AND  | 0  | 0  | 00 |

| OR   | 0  | 0  | 01 |

| Add  | 0  | 0  | 10 |

| Sub  | 0  | 1  | 10 |

| NAND | 1  | 1  | 01 |

| NOR  | 1  | 1  | 00 |