# L1: Introduction to CS6963 and CUDA

January 20, 2010

CS6963

### Outline of Today's Lecture

- Introductory remarks

- · A brief motivation for the course

- · Course plans

- Introduction to CUDA

- Motivation for programming model

- Presentation of syntax

- Simple working example (also on website)

- · Reading:

- CUDA 2.3 Manual, particularly Chapters 2 and 4

- Massively Multicore Programming Book, Chapters 1 and 2

This lecture includes slides provided by:

Wen-mei Hwu (UIUC) and David Kirk (NVIDIA)

see http://courses.ece.illinois.edu/ece498/al/Syllabus.html

3 L1: Course/CUDA Introduction

# CS6963: Parallel Programming for GPUs, MW 10:45-12:05, MEB 3147

- Website: http://www.eng.utah.edu/~cs6963/

- Mailing lists:

- $\underline{cs6963s10\text{-}discussion@list,eng.utah,edu}$  for open discussions on assignments

- cs6963s10-teach@list.eng.utah.edu for communicating with instructors

- · Professor:

Mary Hall

MEB 3466, mhall@cs.utah.edu, 5-1039

Office hours: T 11:00-11:40 AM, W 12:20-1:00 PM (usually), or by appointment

· Teaching Assistant:

Protonu Basu, protonu.basu@utah.edu MEB 3419,

Office hours: TH 10:00-12:00PM

#### **Administrative**

- · Mailing lists:

- <u>cs6963s10-discussion@list.eng.utah.edu</u> for open discussions on assignments

- <u>cs6963s10-teach@list.eng.utah.edu</u> for communicating with instructors

- · First assignment due Wednesday, January 27, 5PM

- Your assignment is to simply add and multiply two vectors to get started writing programs in CUDA. In the regression test (in <u>driver.c</u>). The addition and multiplication are coded into the functions, and the file (<u>CMakeLists.txt</u>) compiles and links

- Use handin on the CADE machines for all assignments

- "handin cs6963 lab1 <probfile>"

- The file <probfile> should be a gzipped tar file of the CUDA program and output

CS6963

L1: Course/CUDA Introduction

### Course Objectives

- Learn how to program "graphics" processors for general-purpose multi-core computing applications

- Learn how to think in parallel and write correct parallel programs

- Achieve performance and scalability through understanding of architecture and software mapping

- · Significant hands-on programming experience

- Develop real applications on real hardware

- · Discuss the current parallel computing context

- What are the drivers that make this course timely

- Contemporary programming models and architectures, and where is the field going

CS6963

L1: Course/CUDA Introduction

#### Outcomes from Last Year's Course

- Paper and poster at Symposium on Application Accelerators for High-Performance Computing <a href="https://saahpc.ncsa.illinois.edu/09/">https://saahpc.ncsa.illinois.edu/09/</a> (late April/early May submission deadline)

- Poster: <u>Assembling Large Mosaics of Electron Microscope Images using GPU</u> -Kannan Venkataraju, Mark Kim, Dan Gerszewski, James R. Anderson, and Mary Hall

- Paper:

- GPU Acceleration of the Generalized Interpolation Material Point Method Wei-Fan Chiang, Michael DeLisi, Todd Hummel, Tyler Prete, Kevin Tew, Mary Hall, Phil Wallstedt, and James Guilkey

- Poster at NVIDIA Research Summit http://www.nvidia.com/object/gpu\_tech\_conf\_research\_summit.html

Poster #47 - Fu, Zhisong, University of Utah (United States)

Solving Eikonal Equations on Triangulated Surface Mesh with CUDA

- · Posters at Industrial Advisory Board meeting

- · Integrated into Masters theses and PhD dissertations

- · Jobs and internships

CS696

L1: Course/CUDA Introduction

#### **Grading Criteria**

Homeworks and mini-projects (4): 30%Midterm test: 15%

• Project proposal: 10%

Project design review: 10% Project presentation/demo 15%

Project final report

20%

CS6963

### Primary Grade: Team Projects

- Some logistical issues:

- 2-3 person teams

- Projects will start in late February

- Three parts:

- (1) Proposal; (2) Design review; (3) Final report and demo

- Application code:

- I will suggest a sample project, an area of future research interest.

- Alternative applications must be approved by me (start early).

CS6963

L1: Course/CUDA Introduction

#### Collaboration Policy

- I encourage discussion and exchange of information between students.

- But the final work must be your own.

- Do not copy code, tests, assignments or written reports.

- Do not allow others to copy your code, tests, assignments or written reports.

CS6963

L1: Course/CUDA Introduction

#### Lab Information

#### Primary lab

- "lab5" in WEB/ "lab6" in WEB

- · Windows machines

- · Accounts are supposed to be set up for all who are registered

- · Contact opers@eng.utah.edu with questions

#### Secondary

• Tesla S1070 system in SCI (Linux) [soon]

## Tertiary

Until we get to timing experiments, assignments can be completed on any machine running CUDA 2.3 (Linux, Windows, MAC OS)

CS696

L1: Course/CUDA Introduction

### A Few Words About Tesla System

Nvidia Tesla system: 240 cores per chip, 960 cores per unit, 32 units.

Over 30,000 cores!

Hosts are Intel Nehalems

PCI+MPI between units

NVIDIA Recognizes University Of Utah As A Cuda Center Of Excellence University of Utah is the Latest in a Growing List of Exceptional Schools Demonstrating Pioneering Work in Parallel (JULY 31, 2008—NVIDIA Corporation)

CS6963

#### Text and Notes

- NVidia, CUDA Programming Guide, available from http://www.nvidia.com/ object/cuda\_develop.html for CUDA 2.3 and Windows, Linux or MAC OS.

- [Recommended] Programming Massively Parallel Processors, Wen-mei Hwu and David Kirk, available from http:// courses.ece.illinois.edu/ece498/al/ Syllabus.html (to be available from Morgan Kaufmann in about 2 weeks!)

- [Additional] Grama, A. Gupta, G. Karypis, and V. Kumar, Introduction to Parallel Computing, 2nd Ed. (Addison-Wesley, 2003).

- Additional readings associated with lectures.

CS6963

L1: Course/CUDA Introduction

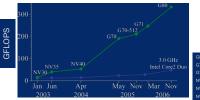

# Why Massively Parallel Processor

- A quiet revolution and potential build-up

- Calculation: 367 GFLOPS vs. 32 GFLOPS

- Memory Bandwidth: 86.4 GB/s vs. 8.4 GB/s

- Until last year, programmed through graphics API

G80 = GeForce 8800 GTX

G71 = GeForce 7900 GTX

G70 = GeForce 7800 GTX

NV40 = GeForce 6800 Ultra

NV35 = GeForce FX 5950 Ultra

NV30 = GeForce FX 5800

GPU in every PC and workstation - massive volume and potential impact

David Kirk/NVIDIA and Wen-mei W. Hwu, 2007 CE 498AL, University of Illinois, Urbana-Champaigi

L1: Course/CUDA Introduction

# GPGPU Concept ot GPGPU (General-Purpose Computing on GPUs)

See http://gpgpu.org

#### · Idea:

- Potential for very high performance at low cost

- Architecture well suited for certain kinds of parallel applications (data parallel)

- Demonstrations of 30-100X speedup over CPU

#### · Early challenges:

- Architectures very customized to graphics problems (e.g., vertex and fragment processors)

- Programmed using graphics-specific programming models or libraries

#### · Recent trends:

- Some convergence between commodity and GPUs and their associated parallel programming models

CS6963

L1: Course/CUDA Introduction

#### CUDA (Compute Unified Device Architecture)

- · Data-parallel programming interface to GPU

- Data to be operated on is discretized into independent partition of memory

- Each thread performs roughly same computation to different partition of data

- When appropriate, easy to express and very efficient parallelization  $% \left( 1\right) =\left( 1\right) \left( 1\right) \left($

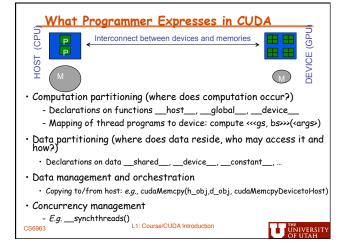

#### Programmer expresses

- Thread programs to be launched on GPU, and how to launch

- Data placement and movement between host and  $\ensuremath{\textit{GPU}}$

- Synchronization, memory management, testing,  $\dots$

- CUDA is one of first to support heterogeneous architectures (more later in the semester)

#### · CUDA environment

-  ${\it Compiler}$ , run-time utilities, libraries, emulation, performance

CS6963

#### Today's Lecture

- · Goal is to enable writing CUDA programs right away

- Not efficient ones need to explain architecture and mapping for that (soon)

- Not correct ones need to discuss how to reason about correctness (also soon)

- Limited discussion of why these constructs are used or comparison with other programming models (more as semester progresses)

- Limited discussion of how to use CUDA environment (more next week)

- No discussion of how to debug. We'll cover that as best we can during the semester.

CS6963

#### CUDA Programming Model: A Highly Multithreaded Coprocessor

- The GPU is viewed as a compute device that:

- Is a coprocessor to the CPU or host

- Has its own DRAM (device memory)

- Runs many threads in parallel

- Data-parallel portions of an application are executed on the device as kernels which run in parallel on many threads

- Differences between GPU and CPU threads

- GPU threads are extremely lightweight

- Very little creation overhead

- GPU needs 1000s of threads for full efficiency

- Multi-core CPU needs only a few

CS6963

L1: Course/CUDA Introduction

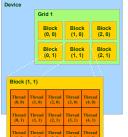

#### Thread Batching: Grids and Blocks A kernel is executed as a grid of thread blocks All threads share data memory space A thread block is a batch of threads that can cooperate with each other by: Synchronizing their execution For hazard-free shared memory accesses Efficiently sharing data through a low latency shared memo Two threads from two different blocks cannot cooperate Courtesy: NDVIA David Kirk/NVIDIA and Wen-mei W. Hwu, 2007 CE 498AL, University of Illinois, Urbana-Champa

#### Block and Thread IDs

- Threads and blocks have IDs

- So each thread can decide what data to work on

- Block ID: 1D or 2D (blockIdx.x, blockIdx.y)

- Thread ID: 1D, 2D, or 3D  $(threadIdx.\{x,y,z\})$

- Simplifies memory addressing when processing multidimensional data

- Image processing

- Solving PDEs on volumes

L1: Course/CLIDA Introduction

Courtesy: NDVIA

· Goal for this example: - Really simple but illustrative of key concepts - Fits in one file with simple compile command - Can absorb during lecture · What does it do? - Scan elements of array of numbers (any of 0 to 9) - How many times does "6" appear? - Array of 16 elements, each thread examines 4 elements, 1 block in grid, 1 grid 7 5 3 5 6 threadIdx.x = 0 examines in\_array elements 0, 4, 8, 12 Known as a threadIdx.x = 1 examines in\_array elements 1, 5, 9, 13 cyclic data threadIdx.x = 2 examines in\_array elements 2, 6, 10, 14 distribution threadIdx.x = 3 examines in\_array elements 3, 7, 11, 15

Simple working code example

#### CUDA Pseudo-Code

#### MAIN PROGRAM:

Initialization

- Allocate memory on host for input and output

- Assign random numbers to input array

Call host function

Calculate final output from per-thread output

Print result

#### GLOBAL FUNCTION:

Thread scans subset of array elements Call device function to compare with "6"

Compute local result

L1: Course/CUDA Introduction

#### **HOST FUNCTION:**

Allocate memory on device for copy of *input* and *output*

Copy input to device Set up grid/block

Call global function

Copy device output to host

#### **DEVICE FUNCTION:**

Compare current element

Return 1 if same, else 0

### Main Program: Preliminaries

#### MAIN PROGRAM:

Initialization

- Allocate memory on host for input and output

- Assign random numbers to input array

Call *host* function

Calculate final output from per-thread output

Print result

#include <stdio.h> #define SIZE 16 #define BLOCKSIZE 4

int main(int argc, char \*\*argv) int \*in\_array, \*out\_array;

CS6963

L1: Course/CUDA Introduction

#### Main Program: Invoke Global Function

# MAIN PROGRAM:

Initialization (OMIT)

- Allocate memory on host for input and output

- Assign random numbers to input array

#### Call host function

Calculate final output from per-thread output

Print result

#include <stdio.h> #define SIZE 16 #define BLOCKSIZE 4

\_\_host\_\_ void outer\_compute (int \*in\_arr, int \*out\_arr); int main(int argc, char \*\*argv)

int \*in\_array, \*out\_array;

/\* initialization \*/ ... outer\_compute(in\_array, out\_array);

L1: Course/CUDA Introduction CS6963

#### Main Program: Calculate Output & Print Result

#### MAIN PROGRAM:

Initialization (OMIT)

Allocate memory on host for input and output Assign random numbers to input array

Call *host* function

Calculate final output from per-thread output

Print result

CS6963

#include <stdio.h> #define SIZE 16 #define BLOCKSIZE 4

\_\_host\_\_ void outer\_compute (int \*in\_arr, int \*out\_arr);

int main(int argc, char \*\*argv)

int \*in\_array, \*out\_array; int sum = 0; /\* initialization \*/ ..

outer\_compute(in\_array, out\_array); for (int i=0; i<BLOCKSIZE; i++) { sum+=out\_array[i];

printf ("Result = %d\n",sum);

###

```

Host Function: Copy Data To/From Host

_host__ void outer_compute (int

*h_in_array, int *h_out_array) {

HOST FUNCTION:

Allocate memory on device for copy of input and output

int *d_in_array, *d_out_array;

Copy input to device

cudaMalloc((void **) &d_in_array,

SIZE*sizeof(int));

Set up grid/block

cudaMalloc((void **) &d_out_array,

BLOCKSIZE*sizeof(int));

Call global function

cudaMemcpy(d_in_array, h_in_array,

SIZE*sizeof(int),

cudaMemcpyHostToDevice);

Copy device output to host

do computation ..

cudaMemcpy(h out_array,d out_array,

BLOCKSIZE*sizeof(int),

cudaMemcpyDeviceToHost);

L1: Course/CUDA Introduction

CS6963

```

```

Host Function: Setup & Call Global Function

HOST FUNCTION:

Allocate memory on device for copy of input and output

Copy input to device

Set up grid/block

Call global function

Copy device output to host

Copy device output to device

Coud Malloc((void **) &d out array,

BLOCKSIZE*sizeof(int));

CoudaMemcpy(d in array, h in array,

BLOCKSIZE*sizeof(int));

CoudaMemcpy(h out array, d out array,

BLOCKSIZE*sizeof(int),

CoudaMemcpy(h out array, d out array,

CoudaMemcpy(h out array, d out array,

BLOCKSIZE*sizeof(int),

CoudaMemcpy(h out arr

```

```

Global Function

GLOBAL FUNCTION:

Thread scans subset of array elements

Call device function to compare with "6"

Compute local result

{

int val = d in[i*BLOCKSIZE + threadIdx.x] + compare(val, 6);

}

}

CS8963

L1: Course/CUDA Introduction

```

#### **Device Function**

# DEVICE FUNCTION:

Compare current element and "6"

Return 1 if same, else 0

```

__device__ int

_compare(int a, int b) {

if (a == b) return 1;

return 0;

}

```

CS6963

L1: Course/CUDA Introduction

#### Reductions

- This type of computation is called a parallel reduction

- Operation is applied to large data structure

- Computed result represents the aggregate solution across the large data structure

- Large data structure → computed result (perhaps single number)

[dimensionality reduced]

- · Why might parallel reductions be well-suited to GPUs?

- · What if we tried to compute the final sum on the GPUs?

CS6963

L1: Course/CUDA Introduction

#### Standard Parallel Construct

- Sometimes called "embarassingly parallel" or "pleasingly parallel"

- · Each thread is completely independent of the others

- · Final result copied to CPU

- · Another example, adding two matrices:

- A more careful examination of decomposing computation into grids and thread blocks

CS6963

L1: Course/CUDA Introduction

#### Summary of Lecture

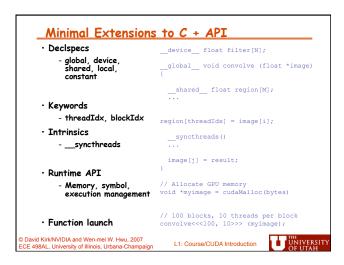

- · Introduction to CUDA

- Essentially, a few extensions to C + API supporting heterogeneous data-parallel CPU+GPU execution

- Computation partitioning

- Data partititioning (parts of this implied by decomposition into threads)

- Data organization and management

- Concurrency management

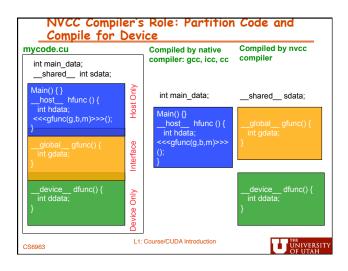

- $\bullet$  Compiler nvcc takes as input a .cu program and produces

- $\emph{C}$  Code for host processor (CPU), compiled by native  $\emph{C}$  compiler

- Code for device processor (GPU), compiled by nvcc compiler

- Two examples

- Parallel reduction

- Embarassingly/Pleasingly parallel computation (your assignment)

CS6963

# Next Week

- · Correctness: Race Conditions & Synchronization (first look)

- · Hardware Execution Model

CS6963