# CS4961 Parallel Programming

# Lecture 3: Introduction to Parallel Architectures

Mary Hall September 1, 2009

09/01/2009

CS4961

# <u>Administrative</u>

- · Homework 1 posted, due September 3 before class

- · Use the "handin" program on the CADE machines

- Use the following command:

- "handin cs4961 hw1 <prob1file>"

- · Waiving C54400 prerequisite, replacing with C53810

- · Textbooks are in bookstore! (as of Friday)

- · What to call me

09/01/2009

CS4961

# Homework 1 - Due 9:10 AM, Thursday, Sept. 3

- · To submit your homework:

- Submit a PDF file

- Use the "handin" program on the CADE machines

- Use the following command: "handin cs4961 hw1 <prob1file>"

- Problem 1:

- What are your goals after this year and how do you anticipate this class is going to help you with that? Some possible answers, but please feel free to add to them. Also, please write at least one sentence of explanation.

- A job in the computing industry

- A job in some other industry where computing is applied to real-world problems

- As preparation for graduate studies  $% \left\{ 1,2,\ldots ,n\right\}$

- Intellectual curiosity about what is happening in the computing field

- Other

CS496

3 THE UNIVERSITY OF UTAH

# Homework 1

- · Problem 2

- Provide pseudocode (as in the book and class notes) for a correct and efficient parallel implementation in C of the parallel sums code, based on the tree-based concept in slides 26 and 27 of Lecture 2. Assume that you have an array of 128 elements and you are using 8 processors.

- Hints

- Use an iterative algorithm similar to count3s, but use the tree structure to accumulate the final result.

- Use the book to show you how to add threads to what we derived for count3s.

- · Problem 3:

- Now show how the same algorithm can be modified to find the maximum element of an array. (problem 2 in text). Is this also a reduction computation? If so, why?

09/01/2009

CS4961

# Questions on Homework?

· Hint: Barrier synchronization (see pgs. 91-92)

09/01/2009 CS4961

# 5 UNIVERSITY

### Today's Lecture

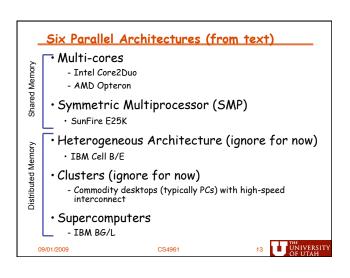

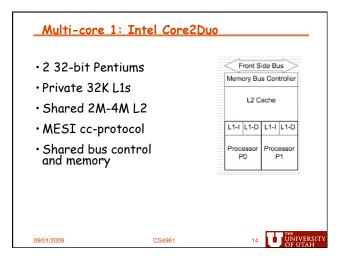

- · Some types of parallel architectures

- SIMD vs. MIMD

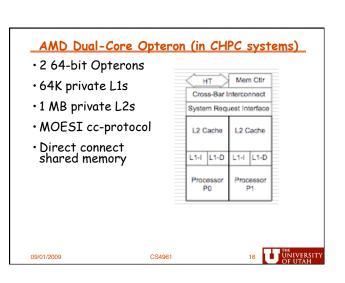

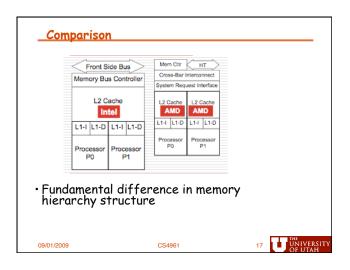

- multi-cores from Intel and AMD

- Sunfire SMP

- BG/L supercomputer

- Clusters

- Later in the semester we'll look at NVIDIA GPUs

- · An abstract architecture for parallel algorithms

- Discussion

- · Sources for this lecture:

- Larry Snyder, "http://www.cs.washington.edu/education/ courses/524/08wi/"

09

S4961

# Why are we looking at a bunch of architectures

- There is no canonical parallel computer a diversity of parallel architectures

- Hence, there is no canonical parallel programming language

- · Architecture has an enormous impact on performance

- And we wouldn't write parallel code if we didn't care about performance

- Many parallel architectures fail to succeed commercially

- Can't always tell what is going to be around in N years

Challenge is to write parallel code that abstracts away architectural features, focuses on their commonality, and is therefore easily ported from one platform to another.

09/01/2009

CS4961

# Retrospective (Jim Demmel)

- Historically, each parallel machine was unique, along with its programming model and programming language.

- It was necessary to throw away software and start over with each new kind of machine.

- Now we distinguish the programming model from the underlying machine, so we can write portably correct codes that run on many machines.

- MPI now the most portable option, but can be tedious.

- Writing portable fast code requires tuning for the architecture.

- Parallel algorithm design challenge is to make this process easy.

- Example: picking a blocksize, not rewriting whole algorithm.

00/04/2000

CS496

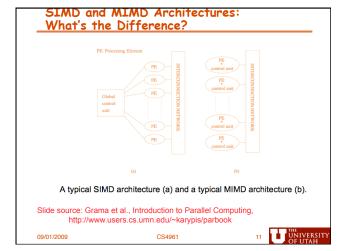

### Predominant Parallel Control Mechanisms

| Name                                             | Meaning                                                                            | Examples                                                        |

|--------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Single Instruction,<br>Multiple Data<br>(SIMD)   | A single thread of<br>control, same<br>computation applied<br>across "vector" elts | Array notation as in<br>Fortran 90:<br>A[1:n] = A[1:n] + B[1:n] |

| Multiple Instruction,<br>Multiple Data<br>(MIMD) | Multiple threads of control, processors periodically synch                         | Parallel loop:<br>forall (i=0; i <n; i++)<="" td=""></n;>       |

| Single Program,<br>Multiple Data<br>(SPMD)       | Multiple threads of<br>control, but each<br>processor executes<br>same code        | Processor-specific code:<br>if (\$myid == 0) {<br>}             |

/01/2009

S4961

UNIVERSITY OF UTAH

# A Few More Words About SIMD (more soon)

- Historically, SIMD architectures at the high end included large vector machines, which are not widely used

- Today SIMD architectures are very popular at a smaller scale

- Multimedia extensions such as Intel SSE-3

- GPUs such as Nvidia Tesla

- Coming: Intel Larrabee

- Interestingly, these architectures use fundamentally different programming models for expressing parallelism

09/01/2009

CS4961

UNIVERSITY OF UTAH

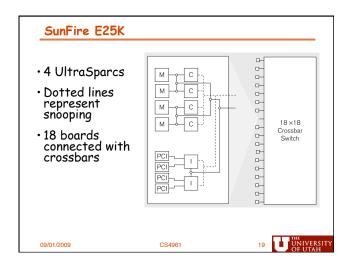

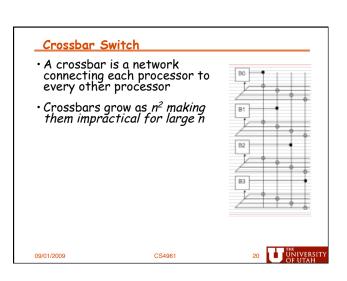

#### Crossbar in SunFire E25K

- X-bar gives low latency for snoops allowing for shared memory

- •18 x 18 X-bar is basically the limit

- Raising the number of processors per node will, on average, increase congestion

- · How could we make a larger machine?

09/01/2009 CS4961 21

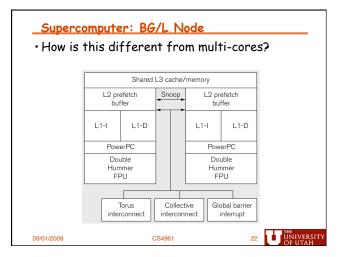

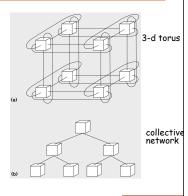

# BG/L Interconnect

- Separate networks for control and data

- Can then specialize network implementation for type of message

- Also reduces congestion

09/01/2009

CS4961

23 THE UNI

# Blue Gene/L Specs

- BG/L was the fastest computer in the world (#1 on the Top500 List) when the textbook was published

- A 64x32x32 torus = 65K 2-core processors

- $\cdot$  Cut-through routing gives a worst-case latency of 6.4  $\mu \rm s$

- Processor nodes are dual PPC-440 with "double hummer" FPUs

- Collective network performs global reduce for the "usual" functions

09/01/2009

CS4961

UNIVERSITY OF UTAH

### Summary of Architectures

#### Two main classes

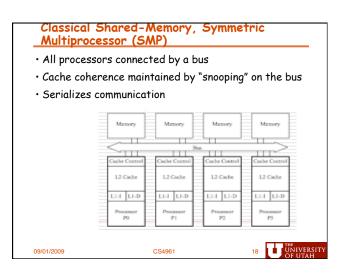

- · Complete connection: CMPs, SMPs, X-bar

- Preserve single memory image

- Complete connection limits scaling to ...

- Available to everyone (multi-core)

- Sparse connection: Clusters, Supercomputers, Networked computers used for parallelism (Grid)

- Separate memory images

- Can grow "arbitrarily" large

- Available to everyone with LOTS of air conditioning

- · Programming differences are significant

09/01/2009

CS4961

25

# THE UNIVERSIT

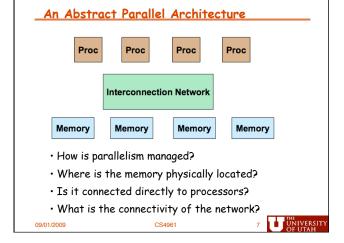

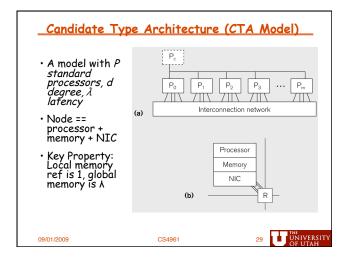

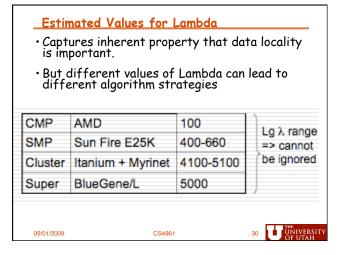

# Parallel Architecture Model

- How to develop portable parallel algorithms for current and future parallel architectures, a moving target?

- Strategy:

- Adopt an abstract parallel machine model for use in thinking about algorithms

- · First step: Review how we use von Neumann

- · Second step: Introduce the CTA

- Third step: Discuss how it relates to today's set of machines

09/01/2009

CS4961

# How did we do it for sequential architectures?

- · The Random Access Machine

- Control, ALU, (Unlimited) Memory, [Input, Output]

- Fetch/execute cycle runs 1 inst. pointed at by PC

- Memory references are "unit time" independent of location

- Gives RAM it's name in preference to von Neumann

- "Unit time" is not literally true, but caches provide that illusion when effective

- Executes "3-address" instructions

- Focus in developing sequential algorithms, at least in courses, is on reducing amount of computation (useful even if imprecise)

- Treat memory time as negligible

- Ignores overheads

# Interesting Historical Parallel Architecture Model, PRAM

- Parallel Random Access Machine (PRAM)

- Unlimited number of processors

- Processors are standard RAM machines, executing synchronously

- Memory reference is "unit time"

- Outcome of collisions at memory specified - EREW, CREW, CRCW ...

- Model fails bc synchronous execution w/ unit cost memory reference does not scale

09/01/2009

CS4961

THE UNI OF I

# **Brief Discussion**

- Why is it good to have different parallel architectures?

- Some may be better suited for specific application domains

- Some may be better suited for a particular community

- Cost

- Explore new ideas

- And different programming models/ languages?

- Relate to architectural features

- Application domains, user community, cost, exploring new ideas

09/01/2009 CS4961

# Summary of Lecture

• Exploration of different kinds of parallel architectures

CS4961

- · Key features

- How processors are connected?

- How memory is connected to processors?

- How parallelism is represented/managed?

- · Models for parallel architectures

09/01/2009

UNIVERSITY OF UTAH