## CS/EE 3810: Computer Organization

# Lecture 13: Branch Prediction & Out-of-order execution

Anton Burtsev November, 2022 **Branch prediction**

#### **Control Hazards**

- Simple techniques to handle control hazard stalls:

- for every branch, introduce a stall cycle (note: every 6<sup>th</sup> instruction is a branch!)

- Assume the branch is not taken and start fetching the next instruction – if the branch is taken, need hardware to cancel the effect of the wrong-path instruction

- Fetch the next instruction (branch delay slot) and execute it anyway – if the instruction turns out to be on the correct path, useful work was done – if the instruction turns out to be on the wrong path, hopefully program state is not lost

- make a smarter guess and fetch instructions from the expected target

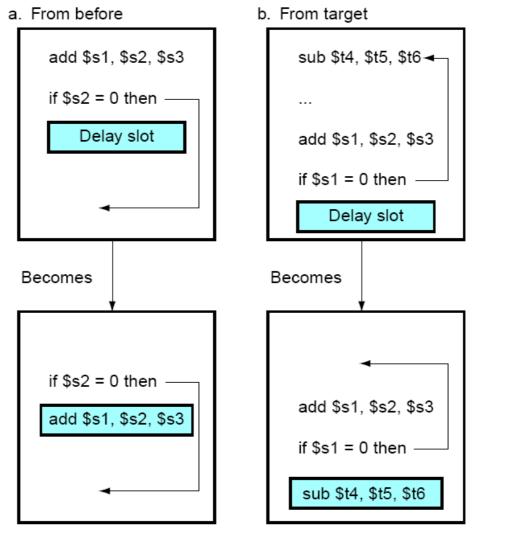

#### **Branch Delay Slots**

Source: H&P textbook

4

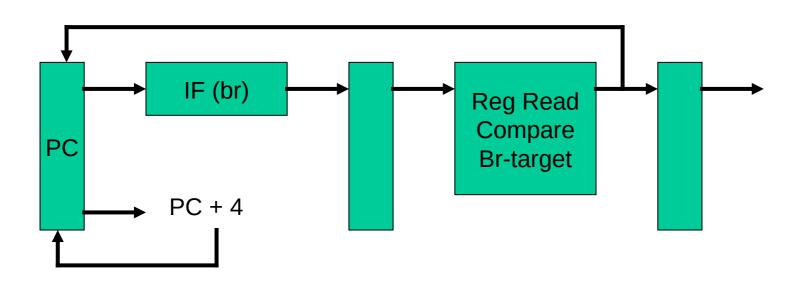

## **Pipeline without Branch Predictor**

In the 5-stage pipeline, a branch completes in two cycles  $\rightarrow$ If the branch went the wrong way, one incorrect instr is fetched  $\rightarrow$ One stall cycle per incorrect branch

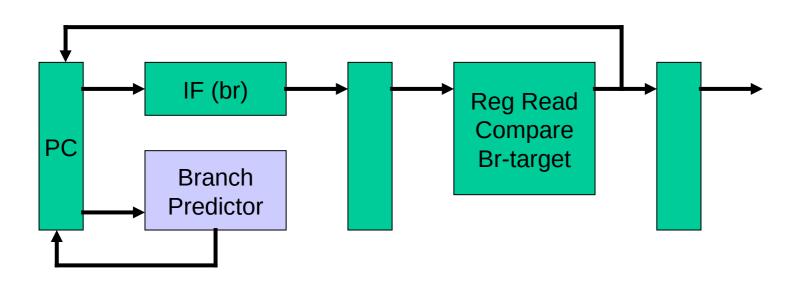

## **Pipeline with Branch Predictor**

In the 5-stage pipeline, a branch completes in two cycles  $\rightarrow$ If the branch went the wrong way, one incorrect instr is fetched  $\rightarrow$ One stall cycle per incorrect branch

## **1-Bit Bimodal Prediction**

- For each branch, keep track of what happened last time and use that outcome as the prediction

- What are prediction accuracies for branches 1 and 2 below:

```

while (1) {

for (i=0;i<10;i++) {

branch-1

...

}

for (j=0;j<20;j++) {

branch-2

...

}

}</pre>

```

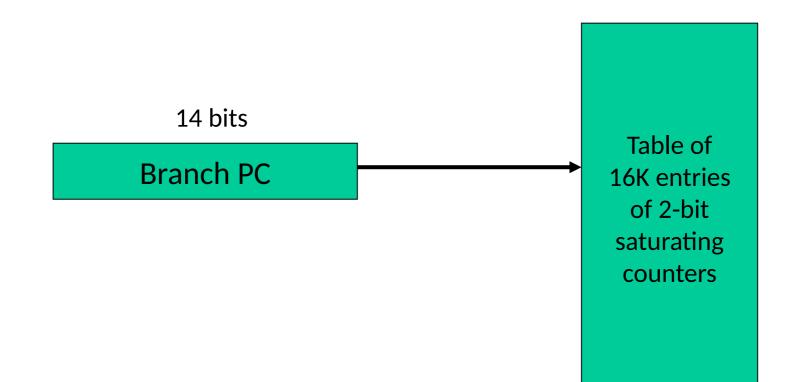

## **2-Bit Bimodal Prediction**

- For each branch, maintain a 2-bit saturating counter: if the branch is taken: counter = min(3,counter+1) if the branch is not taken: counter = max(0,counter-1)

- If (counter >= 2), predict taken, else predict not taken

- Advantage: a few atypical branches will not influence the prediction (a better measure of "the common case")

- Especially useful when multiple branches share the same counter (some bits of the branch PC are used to index into the branch predictor)

- Can be easily extended to N-bits (in most processors, N=2)

#### **Bimodal Predictor**

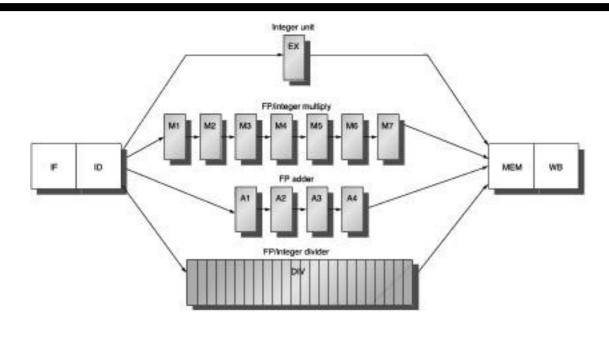

#### **Multicycle Instructions**

© 2003 Elsevier Science (USA). All rights reserved.

- Multiple parallel pipelines each pipeline can have a different number of stages

- Instructions can now complete out of order must make sure that writes to a register happen in the correct order

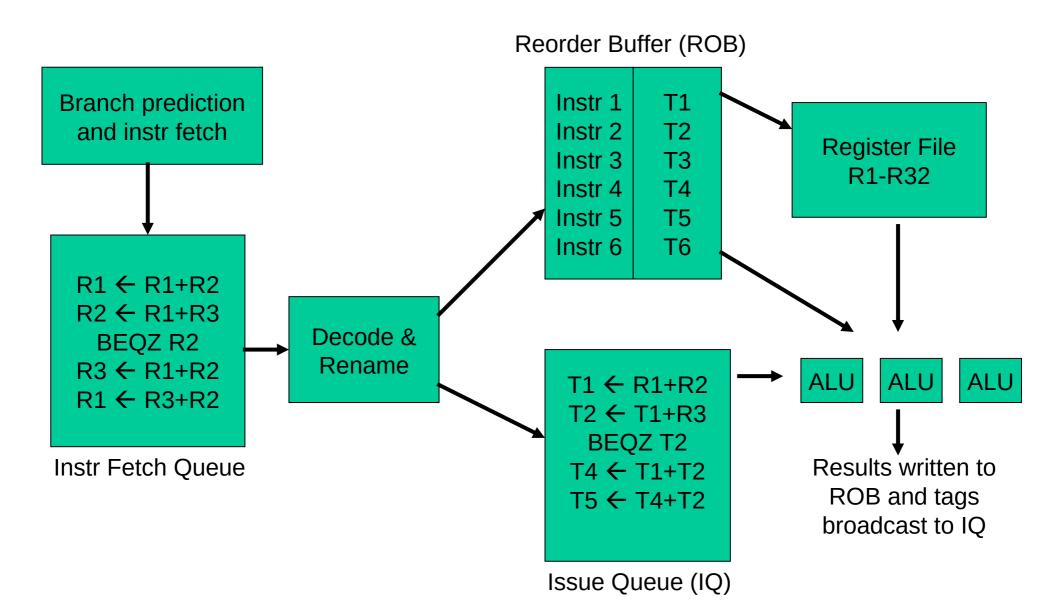

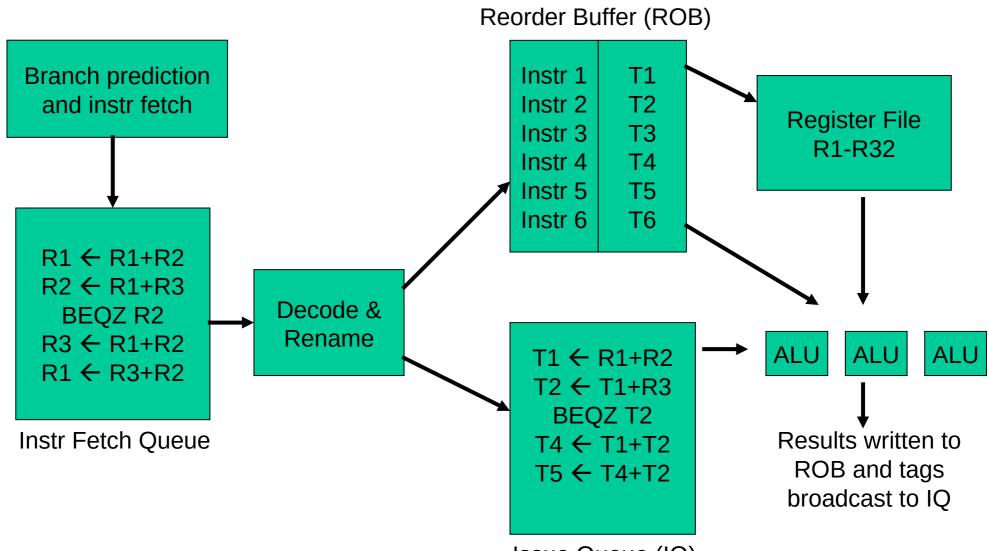

## An Out-of-Order Processor Implementation

#### Example Code

| Completion times | with in-order | with ooo |

|------------------|---------------|----------|

| ADD R1, R2, R3   | 5             | 5        |

| ADD R4, R1, R2   | 6             | 6        |

| LW R5, 8(R4)     | 7             | 7        |

| ADD R7, R6, R5   | 9             | 9        |

| ADD R8, R7, R5   | 10            | 10       |

| LW R9, 16(R4)    | 11            | 7        |

| ADD R10, R6, R9  | 13            | 9        |

| ADD R11, R10, R9 | 14            | 10       |

## An Out-of-Order Processor Implementation

Issue Queue (IQ)

### Design Details - I

- Instructions enter the pipeline in order

- No need for branch delay slots if prediction happens in time

- Instructions leave the pipeline in order all instructions that enter also get placed in the ROB – the process of an instruction leaving the ROB (in order) is called commit – an instruction commits only if it and all instructions before it have completed successfully (without an exception)

- To preserve precise exceptions, a result is written into the register file only when the instruction commits – until then, the result is saved in a temporary register in the ROB

## Design Details - II

- Instructions get renamed and placed in the issue queue some operands are available (T1-T6; R1-R32), while others are being produced by instructions in flight (T1-T6)

- As instructions finish, they write results into the ROB (T1-T6) and broadcast the operand tag (T1-T6) to the issue queue – instructions now know if their operands are ready

- When a ready instruction issues, it reads its operands from T1-T6 and R1-R32 and executes (out-of-order execution)

- Can you have WAW or WAR hazards? By using more names (T1-T6), name dependences can be avoided

## Design Details - III

- If instr-3 raises an exception, wait until it reaches the top of the ROB – at this point, R1-R32 contain results for all instructions up to instr-3 – save registers, save PC of instr-3, and service the exception

- If branch is a mispredict, flush all instructions after the branch and start on the correct path – mispredicted instrs will not have updated registers (the branch cannot commit until it has completed and the flush happens as soon as the branch completes)

- Potential problems: ?

#### Thank you!