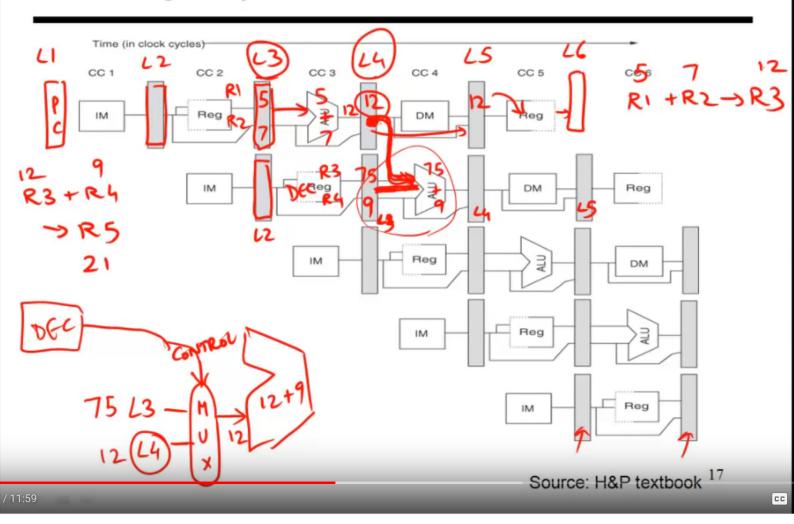

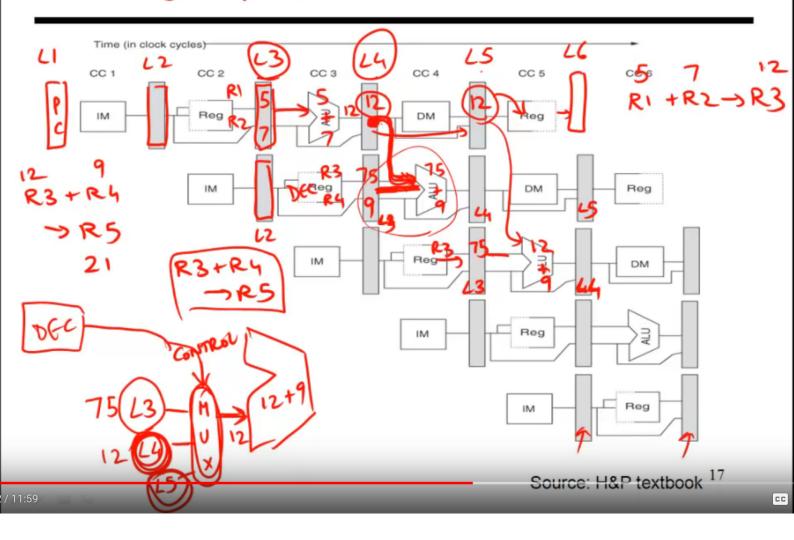

# A 5-Stage Pipeline

### A 5-Stage Pipeline

# Example

# Point of Induction

Source: H&P textbook 19

CC

11:59

Source: H&P textbook 20

CC

/ 11:59

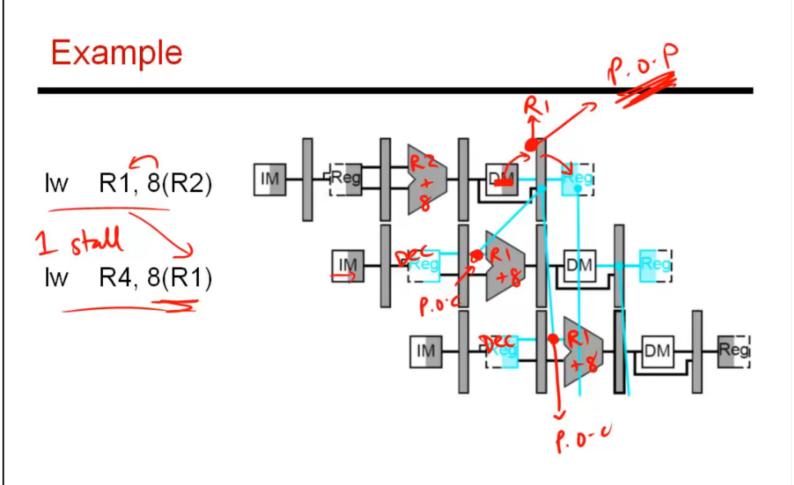

# Example

Source: H&P textbook 21

### Summary

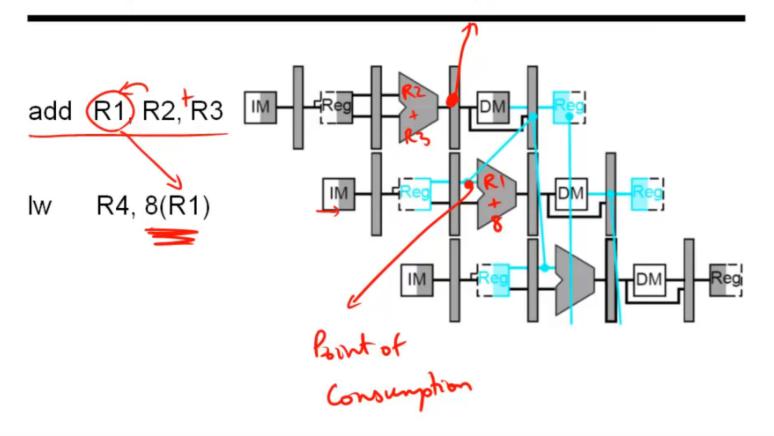

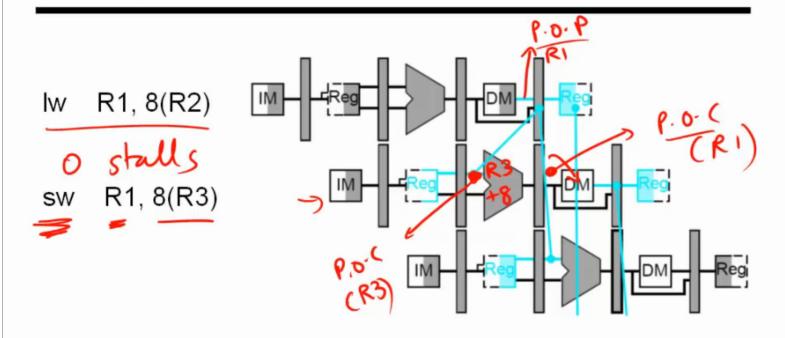

For the 5-stage pipeline, bypassing can eliminate delays between the following example pairs of instructions:

add/sub R1, R2, R3 → P·o·P → 3 √s √s

add/sub/lw/sw R4, R1, R5

Iw R1,8(R2)

$$\rightarrow$$

P.O.P  $\rightarrow$  4th stays

sw R1,4(R3)  $\rightarrow$  P.O.C  $\rightarrow$  4th stays

• The following pairs of instructions will have intermediate stalls:

fmul F1, F2, F3 fadd F5, F1, F4

7 / 11:59

22

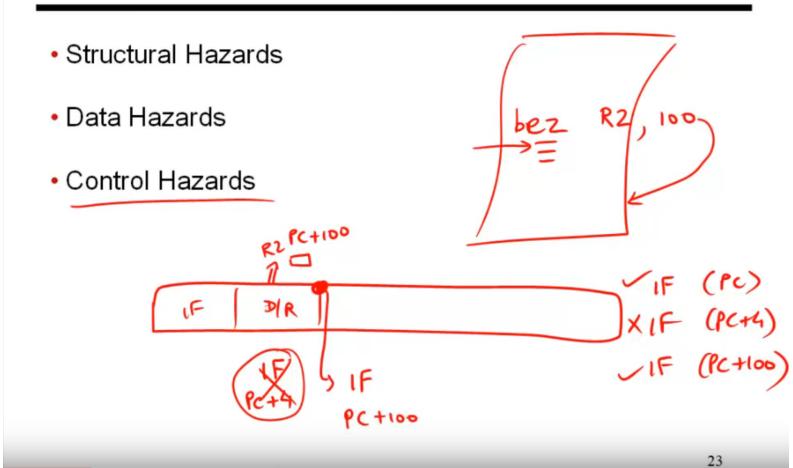

### Hazards

CC

### Control Hazards

- Simple techniques to handle control hazard stalls:

- for every branch, introduce a stall cycle (note: every 6<sup>th</sup> instruction is a branch on average!)

- assume the branch is not taken and start fetching the next instruction if the branch is taken, need hardware to cancel the effect of the wrong-path instructions

- predict the next PC and fetch that instr if the prediction is wrong, cancel the effect of the wrong-path instructions

- fetch the next instruction (branch delay slot) and execute it anyway – if the instruction turns out to be

- on the correct path, useful work was done if the instruction turns out to be on the wrong path,

hopefully program state is not lost

24

/ 11:38

-

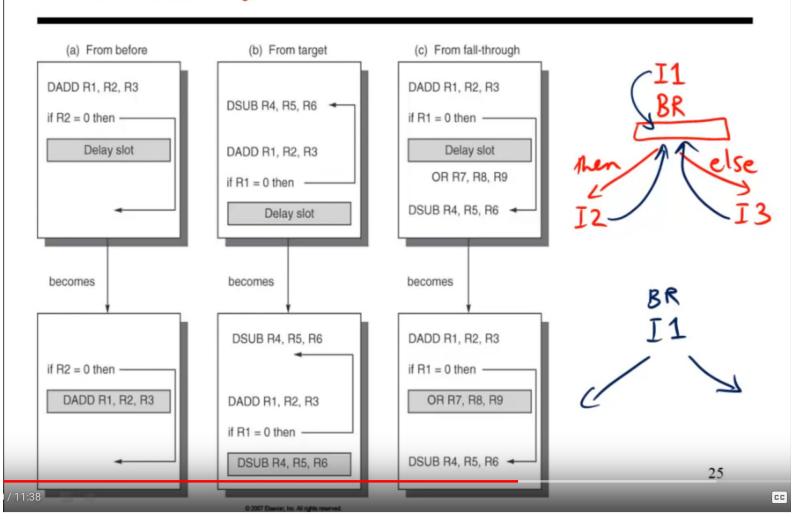

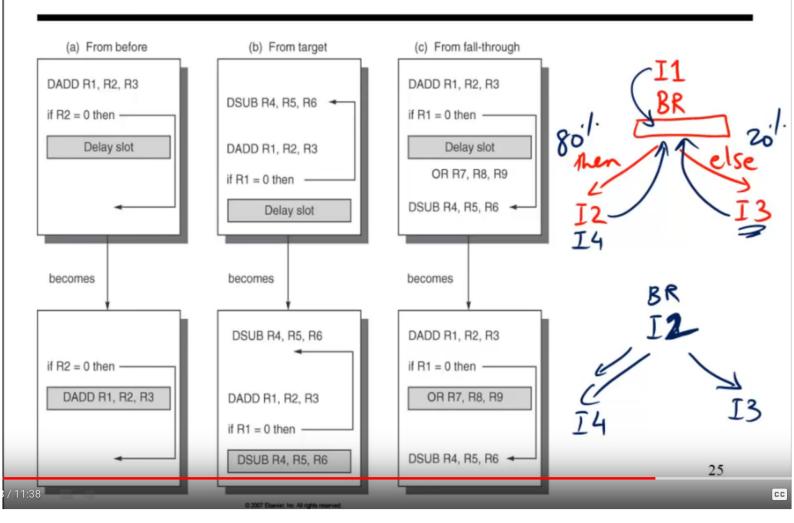

# Branch Delay Slots

# **Branch Delay Slots**

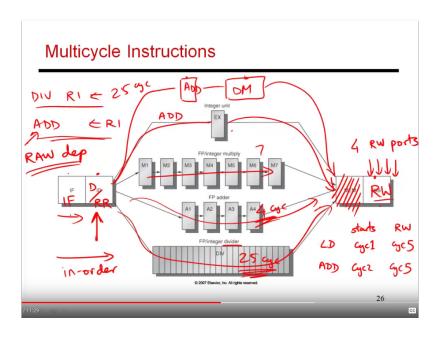

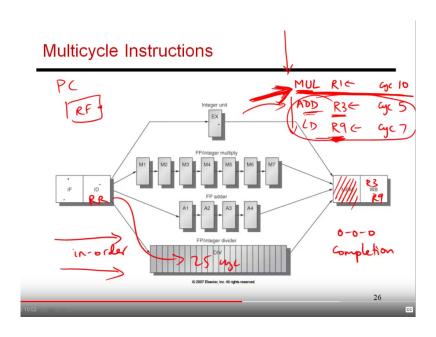

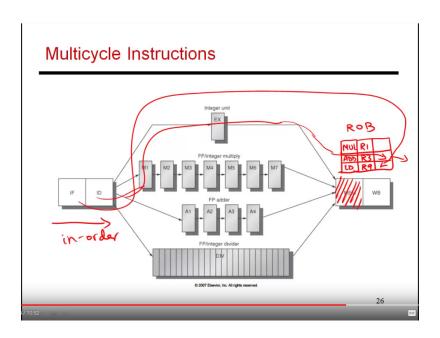

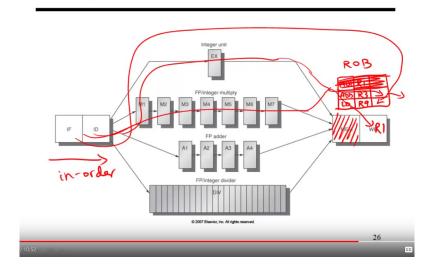

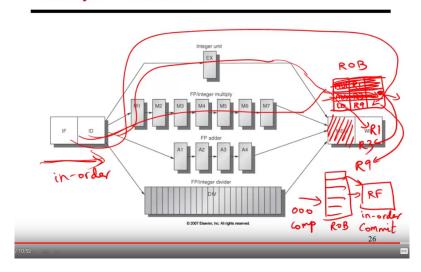

# Effects of Multicycle Instructions Com ERI Potentially multiple writes to the register file in a cycle Frequent RAW hazards WAW hazards (WAR hazards not possible) Wr after Wr Imprecise exceptions because of o-o-o instr completion So Note: Can also increase the "width" of the processor: handle multiple instructions at the same time: for example, fetch two instructions, read registers for both, execute both, etc.

### Effects of Multicycle Instructions

- Potentially multiple writes to the register file in a cycle

- Frequent RAW hazards

- WAW hazards (WAR hazards not possible)

- المالة ا

Note: Can also increase the "width" of the processor: handle multiple instructions at the same time: for example, fetch two instructions, read registers for both, execute both, etc.

27

ſ

### Effects of Multicycle Instructions

Potentially multiple writes to the register file in a cycle ?

II w1

Frequent RAW hazards

WAW hazards (WAR hazards not possible)

RAR

Imprecise exceptions because of o-o-o instr completion

Note: Can also increase the "width" of the processor: handle multiple instructions at the same time: for example, fetch two instructions, read registers for both, execute both, etc.

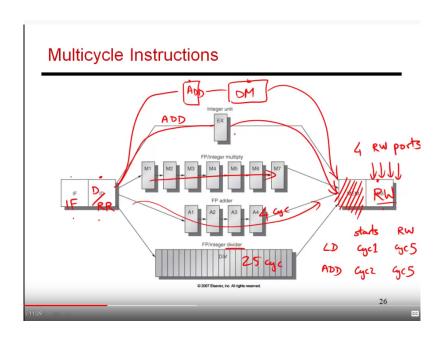

### Multicycle Instructions

### Multicycle Instructions

- Pet Nath

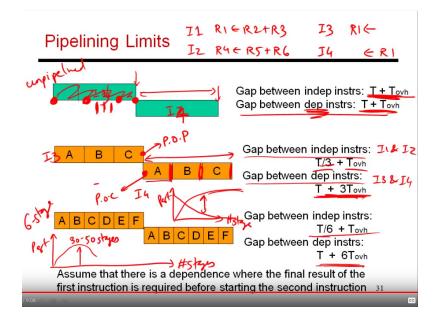

- Perfect pipelining with no hazards → an instruction completes every cycle (total cycles ~ num instructions)

- → speedup = increase in clock speed = num pipeline stages

- With hazards and stalls, some cycles (= stall time) go by during which no instruction completes, and then the stalled instruction completes

- nstruction completes

CPI = 1 + stalls/instruction completes

- Total cycles = number of instructions + stall cycles

12

- Slowdown because of stalls = 1/ (1 + stall cycles per instr)