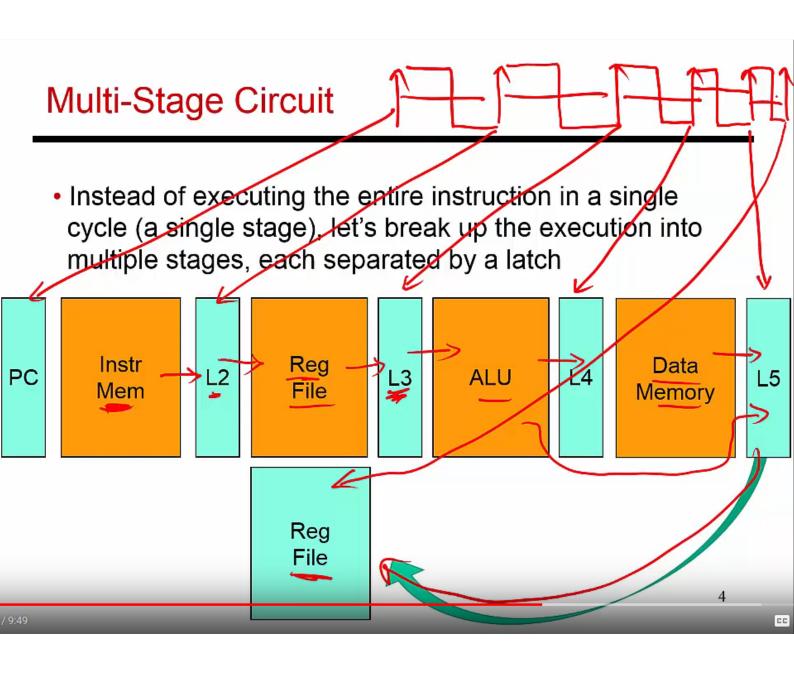

### Clocking Methodology

- Which of the above units need a clock?

- What is being saved (latched) on the rising edge of the clock?

Keep in mind that the latched value remains there for an entire cycle

1:29

5

CC

/ 9:58

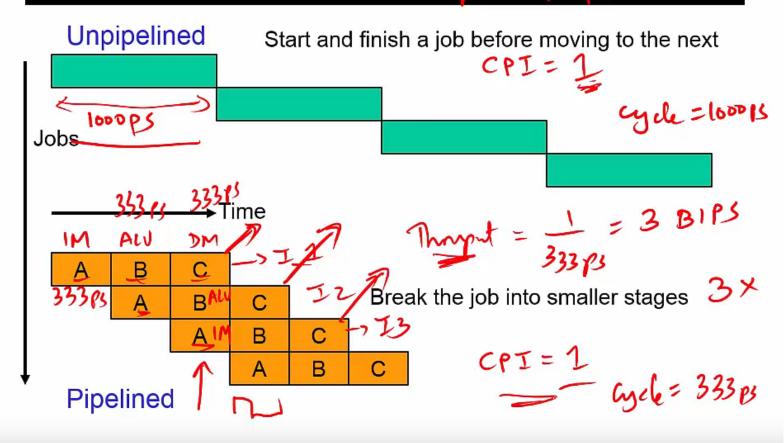

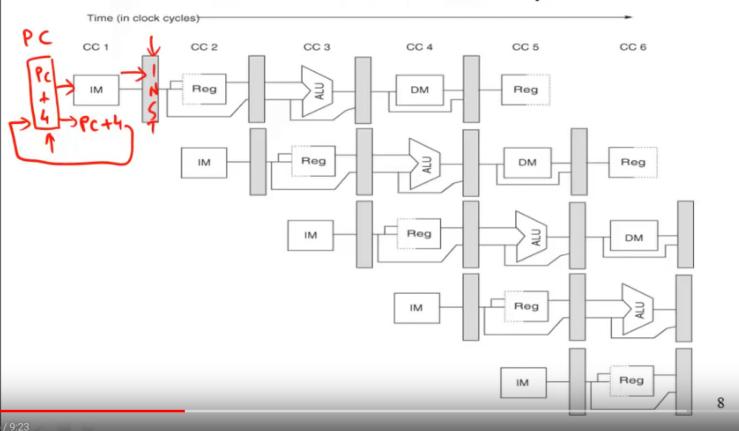

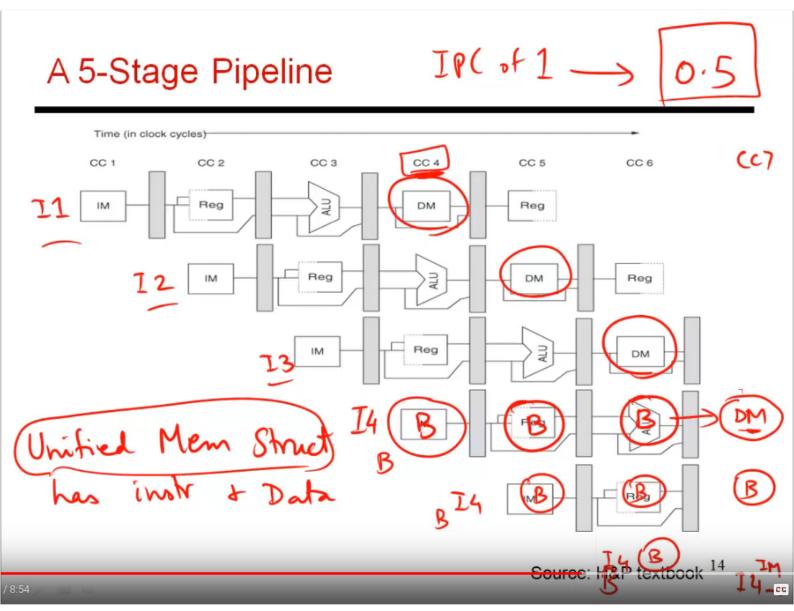

### Performance Improvements?

كالإطمال

Does it take longer to finish each individual job?

- Does it take shorter to finish a series of jobs? 3× +5% 5%

- What assumptions were made while answering these questions?

Is a 10-stage pipeline better than a 5-stage pipeline?

10 > per 5 x 1

10 > per 1

10 > pront 1

11 chips

58

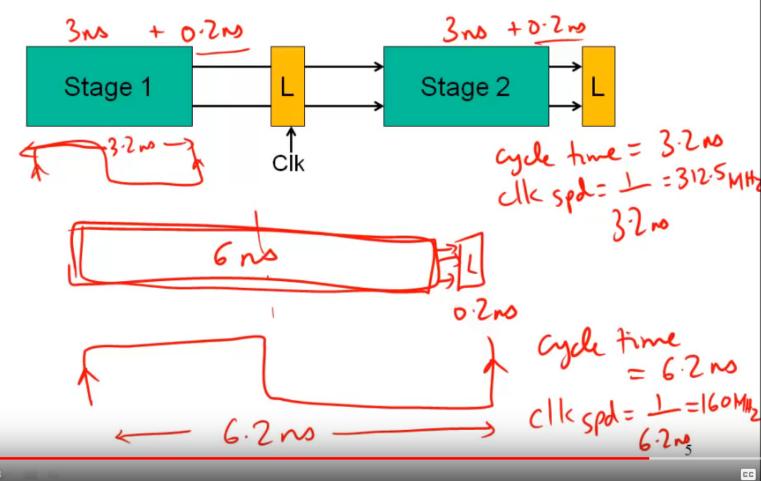

#### Clocks and Latches

11.50

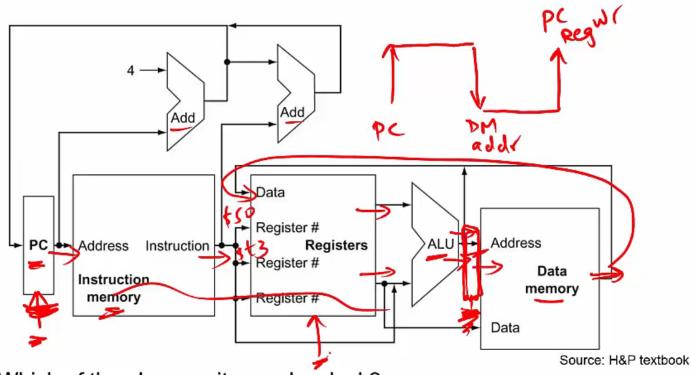

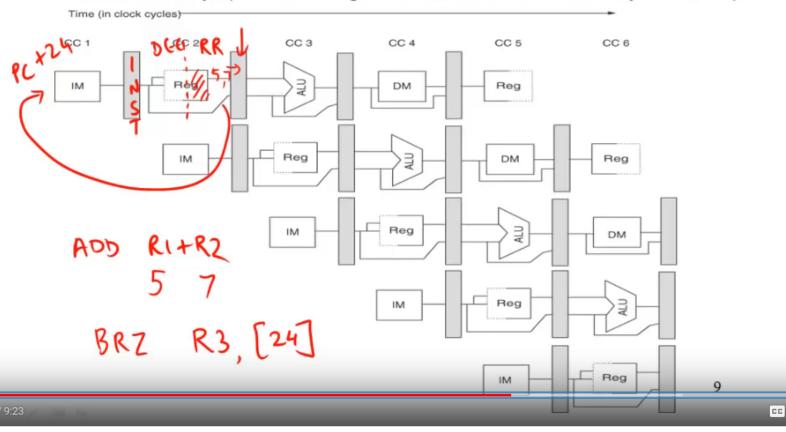

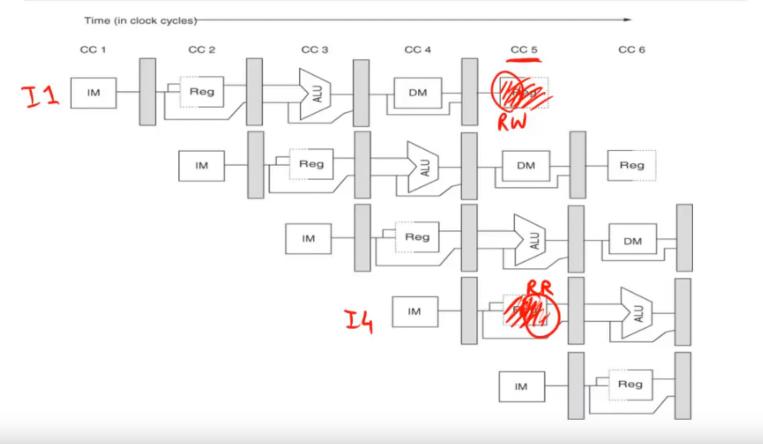

#### Use the PC to access the I-cache and increment PC by 4

CC

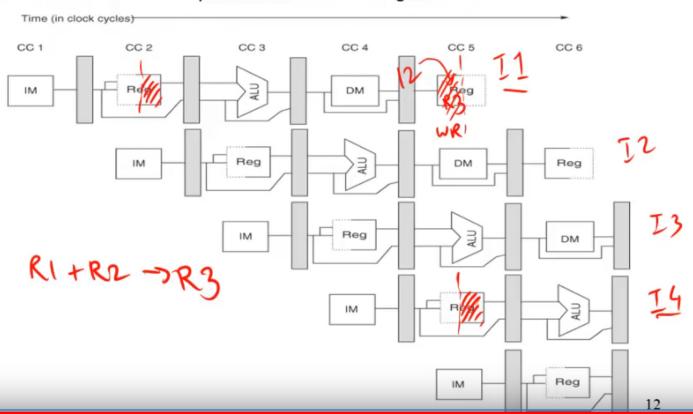

Read registers, compare registers, compute branch target; for now, assume branches take 2 cyc (there is enough work that branches can easily take more)

#### Write result of ALU computation or load into register file

23 <u>cc</u>

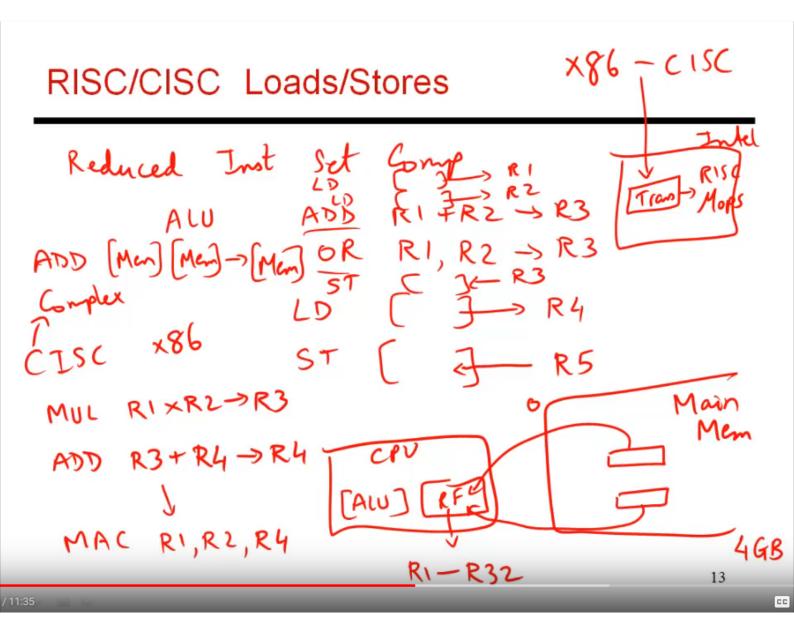

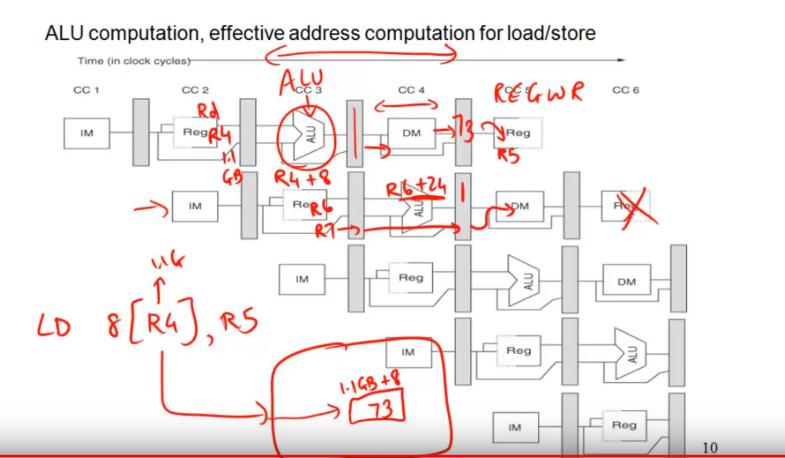

#### RISC/CISC Loads/Stores

11:35

CC

# ST 24[R6], R7

/ 11:35

CC

Source: H&P textbook 14

CC

0.04